半導体技術は、私たちの生活に不可欠な存在です。特にチップレット技術は、次世代の高性能・省電力なシステムを実現する鍵として注目されています。本記事では、チップレット技術と3Dシステムインテグレーションの最新動向を詳しく解説します。

チップレット技術は、異なる回路や製造技術で作られた小さなチップを組み合わせて、1つの機能を実現する方法です。この技術は、従来の単一チップ設計と比較して設計の柔軟性が高く、性能向上と省電力化が期待できます。

さらに、オムロンの高精細・高速インラインCT型検査装置や、SEMICON Japan 2023での最新動向、TSMCとASEの業界協力など、具体的な情報を交えて詳しく解説します。チップレット技術がどのように私たちの未来を変えるのか、その可能性と課題について考察します。

チップレット技術とは何か?

チップレット技術は、半導体業界における革新技術の一つです。この技術は、従来の単一チップ設計から、複数の小さなチップ(チップレット)を組み合わせて機能を実現する方法に移行することを意味します。これにより、設計の柔軟性が増し、性能向上と省電力化が可能となります。特に、異なる製造技術や回路を組み合わせることで、より高性能なシステムを構築することができます。

チップレット技術の一つの大きな利点は、製造コストの削減です。従来のモノリシックチップは、製造過程での不良率が高くなるとコストが急増するという課題がありました。しかし、チップレットを使用することで、個々のチップの歩留まりを向上させることができます。また、チップレット同士を標準化されたインターフェースで接続することで、開発時間とコストを大幅に削減できます。

さらに、チップレット技術は、システムのアップグレードやカスタマイズが容易になるという利点もあります。例えば、特定の機能を強化したい場合、その機能を持つチップレットだけを交換することが可能です。これにより、製品のライフサイクルが延び、顧客に対して柔軟なソリューションを提供することができます。このように、チップレット技術は、ビジネスにおいても大きなメリットをもたらすものとして期待されています。

チップレット技術は、ムーアの法則が限界に達しつつある現代において、重要な役割を果たします。半導体の微細化が進む中で、製造の難易度とコストが増加していますが、チップレット技術を活用することで、この課題に対応できます。今後、さらに多くの企業がこの技術を採用し、新しい半導体製品を開発することが予想されます。

チップレット技術の背景と必要性

チップレット技術の登場は、半導体業界の長年の課題を解決するためのものです。ムーアの法則が示すように、トランジスタの密度は2年ごとに倍増するとされていますが、微細化が進むにつれ、その実現はますます難しくなっています。このため、新しいアプローチが求められていました。チップレット技術は、その解決策として注目されるようになりました。

従来のモノリシックチップ設計では、製造プロセスの複雑さと高コストが問題となっていました。特に高性能な半導体を製造する際、歩留まりの低下がコストを押し上げる要因となっていました。チップレット技術は、これらの課題を解決するために、個々の機能を持つ小さなチップレットを組み合わせて1つのシステムを構築する方法を採用しています。これにより、製造プロセスの効率化とコスト削減が可能となります。

さらに、チップレット技術は、異なる技術や材料を組み合わせることができるため、性能と信頼性の向上にも寄与します。例えば、ある機能に特化した先端技術を持つチップレットを他の機能と組み合わせることで、システム全体の性能を最大化することができます。また、製造後に特定のチップレットを交換することで、製品のアップグレードや修理が容易になります。これにより、製品寿命の延長とメンテナンスコストの削減が実現します。

チップレット技術の必要性は、今後さらに増大すると予想されます。特に、AIやIoTの普及に伴い、より高性能で省電力な半導体が求められる中で、チップレット技術はその要件を満たす重要な手段となります。企業はこの技術を活用することで、競争力を高め、持続可能なビジネスモデルを構築することができます。このように、チップレット技術の背景には、現代の技術的課題と市場ニーズの変化があるのです。

高精細・高速インラインCT型検査装置の役割

オムロンが開発した高精細・高速インラインCT型検査装置は、チップレット技術の品質保証において重要な役割を果たしています。この装置は、0.2μmの高分解能でチップレットのはんだ品質を可視化し、3D実装で使用されるμBumpやC4Bumpの検査を可能にします。これにより、製造過程での不良を早期に発見し、製品の信頼性を確保することができます。

具体的には、この検査装置はリアルタイムでの高精度な検査を行うことで、製造ラインの効率を向上させます。従来の検査方法では見逃されがちな微細な欠陥も、この装置を使用することで確実に検出することができます。これにより、製品の品質を向上させるとともに、歩留まりの改善にも寄与します。特に、医療用CTスキャン技術を応用した高精細な画像解析が可能であるため、半導体業界における品質管理の新たな基準を提供しています。

さらに、このインラインCT型検査装置は、製造プロセスの一部として組み込むことができるため、リアルタイムでの監視と即時の対応が可能です。これにより、製造工程全体の効率化が図られ、コスト削減にもつながります。特に、複雑化する3Dシステムインテグレーションにおいては、各チップレットの品質を確保するための信頼性の高い検査が求められており、この装置がそのニーズに応えています。

オムロンの高精細・高速インラインCT型検査装置は、チップレット技術の進化を支える重要な要素となっています。この装置を導入することで、企業は製品の品質を高めるとともに、製造コストの削減と生産効率の向上を実現することができます。今後も、このような先端技術の導入が、半導体業界全体の競争力を高める鍵となるでしょう。

3Dシステムインテグレーションの革新

3Dシステムインテグレーション(3D-SI)は、チップレット技術と組み合わせることで、半導体業界に革新をもたらしています。この技術は、異なる回路や機能を持つチップレットを3次元的に積層することで、高性能かつ省電力なシステムを実現します。特に、異なるプロセス技術や材料を統合できるため、設計の自由度が飛躍的に向上します。

具体的な例として、SEMICON Japan 2023で発表された設計環境では、異種のチップレットを同一のインタポーザ上に3D実装することで、システム全体の機能と動作を効率的に検証できます。これにより、従来の2Dパッケージングでは実現が難しかった高度なシステム統合が可能となり、製品の性能と信頼性が大幅に向上します。また、この技術は、新しいアプリケーションや用途に対して迅速に対応するための柔軟性を提供します。

さらに、3Dシステムインテグレーションは、スペース効率の向上にも寄与します。複数のチップレットを垂直に積み重ねることで、基板上の占有面積を減少させることができます。これにより、小型化が求められるデバイスや機器の設計において大きなメリットが生まれます。例えば、スマートフォンやウェアラブルデバイスなど、限られたスペースに多機能を集約する必要がある製品において、3D-SIは不可欠な技術となっています。

3Dシステムインテグレーションの革新は、製品の性能向上だけでなく、エネルギー効率の向上にも貢献します。チップレット間の距離が短くなることで、信号伝達の遅延が減少し、消費電力が抑えられます。これにより、エネルギー効率の高いシステム設計が可能となり、環境負荷の低減にもつながります。今後も、3D-SI技術の進化により、さらに高度なシステムインテグレーションが実現することでしょう。

SEMICON Japan 2023の最新動向

SEMICON Japan 2023は、半導体業界における最新技術とトレンドを紹介する重要なイベントです。今年の注目は、チップレット技術と3Dシステムインテグレーションに関する発表でした。このイベントでは、最新の設計環境や製造技術が紹介され、業界関係者にとって非常に有益な情報が提供されました。特に、異種の回路技術を組み合わせた高度なパッケージングソリューションが焦点となりました。

具体的には、異なる製造技術で作成されたチップレットを同じインタポーザ上に3Dで実装する設計環境が紹介されました。これにより、システム全体の機能と動作を効率的に検証できる新しいアプローチが提案されました。この技術は、製品の性能と信頼性を大幅に向上させると同時に、設計の柔軟性を高めることができます。また、この技術は、次世代の半導体製品の開発において重要な役割を果たすと期待されています。

さらに、SEMICON Japan 2023では、チップレット技術の実装における課題とその解決策についても議論されました。特に、インターポーザの材料選定や、チップレット間の通信効率を向上させるための新しい接続技術が紹介されました。これらの技術革新は、チップレット技術の実用化を加速させるとともに、製品の市場投入を迅速にするための鍵となります。また、これらの議論は、業界全体の技術力向上に寄与します。

このように、SEMICON Japan 2023は、チップレット技術と3Dシステムインテグレーションの未来を探る上で非常に重要な情報源となりました。参加者は、最新の技術動向を把握するとともに、業界のトップランナーたちと意見交換を行うことができました。今後も、このようなイベントが技術革新の推進力となり、半導体業界全体の成長を支えることが期待されます。

異種技術の統合によるシステム最適化

異種技術の統合は、現代の半導体技術において不可欠な要素となっています。特に、チップレット技術と3Dシステムインテグレーションの組み合わせにより、異なる回路や製造技術を一つのシステムに統合することが可能です。このアプローチにより、システムの性能を最大限に引き出し、製造コストを削減することができます。また、異なる技術の統合は、設計の柔軟性を飛躍的に向上させます。

具体的な例として、TSMCやASEなどの大手半導体メーカーが、異種技術の統合に積極的に取り組んでいます。彼らは、異なる技術を持つチップレットを一つのインタポーザに統合し、高性能なシステムを実現しています。例えば、デジタル回路とアナログ回路、さらにはMEMS技術を組み合わせることで、新しい機能を持つ製品が開発されています。これにより、製品の多様化と高性能化が実現します。

さらに、異種技術の統合は、製品の信頼性と寿命を向上させる効果もあります。異なる技術を組み合わせることで、各技術の強みを活かし、弱点を補うことができます。例えば、高耐久性の材料を使用することで、製品の耐久性を向上させる一方で、最新のプロセス技術を導入することで性能を最大化します。これにより、製品のトータルコストパフォーマンスが向上し、競争力が強化されます。

最後に、異種技術の統合は、新しい市場やアプリケーションに対応するための重要な手段となります。特に、IoTやAI、5Gといった新興技術分野では、複雑な機能を統合することが求められます。異種技術を統合することで、これらの市場のニーズに迅速に対応し、先進的な製品を提供することが可能となります。今後も、異種技術の統合が半導体業界の成長を牽引する重要な要素となるでしょう。

TSMCとASEの業界協力の重要性

TSMCとASEの業界協力は、チップレット技術の進展において極めて重要です。両社は、それぞれの強みを生かして新しいソリューションを提供しています。TSMCは世界最大の半導体受託製造企業であり、最先端のプロセス技術を提供しています。一方、ASEは先進的なパッケージング技術を持ち、これらを組み合わせることで高性能なチップレット製品が生まれます。

この協力関係は、チップレット間のインターフェースの標準化にも寄与しています。標準化により、異なるメーカーが製造したチップレットを同じシステム内で互換性を持って使用することが可能になります。これにより、設計の柔軟性が増し、開発時間の短縮とコスト削減が実現します。また、業界全体の技術進歩を促進し、新たなイノベーションを生む土壌が形成されます。

さらに、TSMCとASEの協力は、3Dシステムインテグレーションの分野でも大きな成果を上げています。例えば、TSMCの先進的なプロセス技術とASEの高度なパッケージング技術を組み合わせた製品は、より高性能かつ省電力な半導体を実現します。これにより、次世代のAIやIoTデバイスの開発が加速し、さまざまな産業において競争力を高めることができます。

この協力はまた、環境への配慮にも繋がっています。省電力で高性能な半導体製品を提供することで、エネルギー消費を抑え、環境負荷の低減に貢献します。持続可能な社会の実現に向けて、TSMCとASEの取り組みは重要な一歩となります。これらの要素を総合的に考慮すると、両社の業界協力は半導体業界全体の発展に大きく寄与することがわかります。

ケイデンスのIntegrity 3D-ICプラットフォーム

ケイデンスのIntegrity 3D-ICプラットフォームは、チップレット技術と3Dシステムインテグレーションの実現において重要なツールとなっています。このプラットフォームは、複雑な3Dデザインを効率的に管理し、設計者が高性能なシステムを迅速に構築できるよう支援します。特に、異なる技術や材料を統合する際の設計の柔軟性を提供します。

具体的には、Integrity 3D-ICプラットフォームは、高度なシミュレーション機能を備えており、設計の初期段階から最終検証までの全プロセスをサポートします。これにより、設計ミスを減少させ、製品の品質を向上させることができます。また、熱管理や電力供給の最適化といった重要な設計要素も統合的に管理できるため、全体の性能を最大化することができます。

さらに、このプラットフォームは、チップレット間のインターフェースを標準化するためのツールも提供しています。標準化されたインターフェースにより、異なるメーカーが製造したチップレットを一つのシステム内で効率的に統合できます。これにより、製造コストの削減と開発スピードの向上が実現し、マーケット投入までの時間を大幅に短縮することができます。

ケイデンスのIntegrity 3D-ICプラットフォームは、持続可能な設計を支援する機能も備えています。エネルギー効率の高い設計を可能にすることで、環境負荷を低減し、持続可能な社会の実現に貢献します。これにより、企業は環境規制を遵守しつつ、高性能な製品を提供することができます。このように、Integrity 3D-ICプラットフォームは、チップレット技術の進化を支える強力なツールであり、未来の半導体設計に不可欠な存在となるでしょう。

日本企業がリードするチップレット技術

日本企業は、チップレット技術の分野で重要な役割を果たしています。特に、オムロンや東芝などの大手企業は、先進的な技術開発に力を入れており、世界市場における競争力を高めています。これらの企業は、高精度な製造技術や品質管理のノウハウを活かして、チップレット技術の進展をリードしています。

オムロンは、0.2μmの高分解能を持つインラインCT型検査装置を開発し、チップレットの品質保証において大きな貢献をしています。この装置は、3D実装の検査を高速かつ正確に行うことができ、製品の信頼性を確保します。また、東芝は、異なる技術を統合するための高度なパッケージング技術を提供しており、これにより高性能な半導体製品の開発が可能となっています。

さらに、日本企業は、環境に配慮した製品開発にも積極的です。省電力技術やリサイクル可能な材料の使用など、持続可能な社会の実現に向けた取り組みを進めています。これにより、企業は環境規制を遵守しつつ、高品質な製品を提供することができます。また、これらの取り組みは、企業のブランド価値を高め、消費者の信頼を得ることに繋がります。

日本企業の強みは、技術力だけでなく、細部へのこだわりと品質への妥協を許さない姿勢にあります。これらの要素が組み合わさることで、チップレット技術の分野においても、日本企業は確固たる地位を築いています。今後も、これらの企業はイノベーションを続け、世界市場でのリーダーシップを維持することでしょう。

チップレット技術の将来展望と課題

チップレット技術は、今後も進化を続けると予想されます。この技術の将来展望には、さらに高性能で省電力なシステムの実現が含まれています。特に、AIやIoT、5Gといった次世代のテクノロジーとの組み合わせにより、新しいアプリケーションが次々と生まれるでしょう。これにより、さまざまな産業分野での活用が期待されます。

しかし、チップレット技術の普及にはいくつかの課題も存在します。まず、異なるメーカーが製造したチップレット間のインターフェースの標準化が不可欠です。この標準化が進まなければ、異なるチップレットを統合する際に互換性の問題が発生し、システム全体の性能が低下する恐れがあります。また、標準化が進むことで、開発コストの削減と製品の迅速な市場投入が可能となります。

また、チップレット技術の製造プロセス自体も高度な技術を必要とします。微細化が進む中で、製造精度の向上と不良率の低減が求められます。これには、高度な製造装置や検査技術の導入が不可欠です。例えば、オムロンのインラインCT型検査装置のような高精度な検査技術が、製品の品質を保証するために重要な役割を果たします。

さらに、環境への配慮も重要な課題です。省電力技術の開発と共に、リサイクル可能な材料の使用や製造プロセスの効率化が求められます。これにより、持続可能な社会の実現に貢献すると共に、企業の社会的責任を果たすことができます。チップレット技術の進展には、これらの課題を克服するための継続的なイノベーションが必要です。

具体的な事例:成功したチップレット実装

成功したチップレット実装の具体例として、AMDのRyzenプロセッサが挙げられます。Ryzenプロセッサは、複数のチップレットを組み合わせて一つのプロセッサとして機能させる設計を採用しています。このアプローチにより、高性能とコスト効率を両立させることができ、消費者市場で大きな成功を収めました。特に、ゲームやクリエイティブワークにおいて、Ryzenプロセッサはその性能の高さが評価されています。

また、インテルもチップレット技術を活用した製品を開発しています。インテルのFoverosテクノロジーは、異なるプロセス技術で製造されたチップレットを3D積層することで、性能と省電力性を両立させています。この技術は、次世代のモバイルデバイスやデータセンター向けプロセッサに応用されており、その柔軟性と効率性が注目されています。特に、インテルのLakefieldプロセッサは、Foveros技術を用いて小型化と高性能化を実現しています。

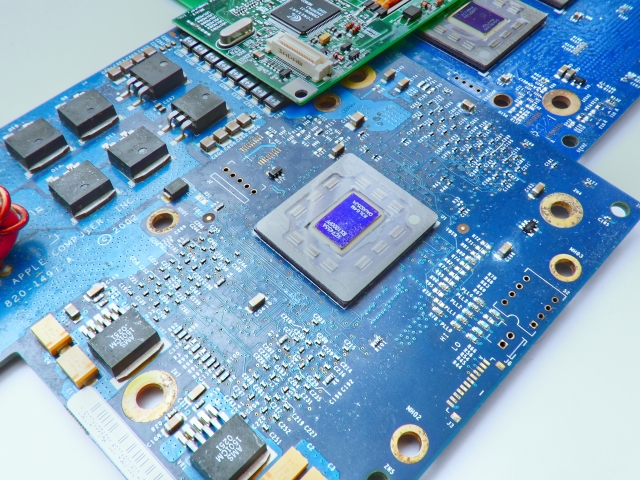

さらに、アップルのM1チップもチップレット技術の成功例です。M1チップは、CPU、GPU、AIアクセラレータなどを一つのパッケージに統合し、高い性能と省電力性を実現しています。この統合設計により、アップルはMacシリーズの性能を大幅に向上させ、エネルギー効率の向上にも成功しました。また、チップレット技術を活用することで、製品の設計自由度が増し、新しい機能の追加が容易になっています。

これらの成功例からわかるように、チップレット技術は高性能かつ省電力な製品を実現するための強力なツールです。企業はこの技術を活用することで、競争力を高め、市場での成功を収めることができます。今後も、チップレット技術を取り入れた製品が続々と登場し、半導体業界全体の進化を促進するでしょう。

チップレット技術の可能性と今後の展望

チップレット技術は、半導体業界において革新をもたらす重要な要素です。これまでに紹介したように、さまざまな成功事例が示すように、チップレット技術は高性能で省電力なシステムを実現するための鍵となります。この技術は、製品の設計自由度を高め、製造コストの削減や製品の信頼性向上に寄与します。特に、異なる技術や材料を効率的に統合できる点が大きな魅力です。

しかし、チップレット技術の普及にはいくつかの課題も存在します。異なるメーカーが製造したチップレット間のインターフェースの標準化が進まないと、互換性の問題が発生する可能性があります。また、高度な製造技術と検査技術の導入が必要であり、これには多大な投資が求められます。さらに、省電力で環境に配慮した製品開発が求められており、持続可能な社会の実現に向けた取り組みが不可欠です。

今後、チップレット技術はさらに進化し、AIやIoT、5Gといった次世代のテクノロジーとの連携が進むことで、新たなアプリケーションが生まれるでしょう。これにより、さまざまな産業分野での活用が期待されます。また、異種技術の統合によるシステム最適化や高精度な検査装置の導入が進むことで、製品の品質と性能が一層向上します。企業は、これらの技術革新を積極的に取り入れ、競争力を維持することが重要です。

総じて、チップレット技術は半導体業界の未来を切り拓く革新的な技術です。企業はこの技術を活用し、持続可能なイノベーションを追求することで、市場での競争優位を確立できます。今後もチップレット技術の進展に注目し、その可能性を最大限に活用することが求められます。