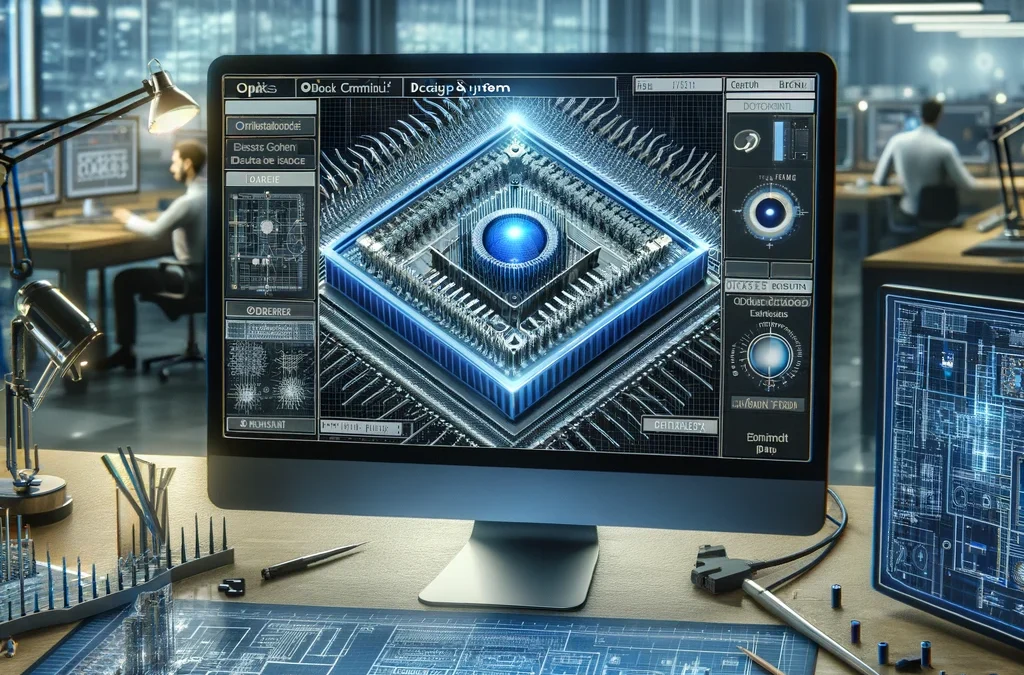

3D半導体パッケージングは、半導体技術の革新を象徴する重要な進展です。この技術は、性能向上とコスト削減を同時に達成することを可能にし、多くの産業で応用されています。本記事では、3Dパッケージングの技術的背景とビジネスインパクトについて詳述します。

3D半導体パッケージングとは?

3D半導体パッケージングは、複数の半導体チップを垂直に積み重ねて統合する技術です。従来の2Dパッケージングでは、チップは平面的に配置されていましたが、3Dパッケージングでは垂直方向に配置されるため、より高い集積度と性能を実現できます。これにより、より小型で高性能なデバイスが可能となり、エレクトロニクス業界に革新をもたらしています。

この技術は、メモリチップやプロセッサなどの多様な用途に使用されており、デバイス間の通信距離が短縮されるため、信号遅延が減少し、全体的なシステム性能が向上します。また、エネルギー効率も向上するため、低消費電力が求められるモバイルデバイスやIoTデバイスにとっても重要な技術です。

3D半導体パッケージングには、シリコン貫通ビア(TSV: Through-Silicon Via)技術が利用されます。TSVは、チップ間を垂直に接続するための微細な穴を形成し、電気的に接続する技術です。この技術により、チップ間のデータ転送速度が向上し、パッケージング全体の効率が向上します。さらに、3Dパッケージングは、製造コストの削減や製造プロセスの簡略化にも寄与します。

現在、3D半導体パッケージングは、AI、高性能コンピューティング(HPC)、データセンターなどの分野での応用が進んでおり、その重要性はますます高まっています。

技術の進化の歴史

3D半導体パッケージングの技術は、1990年代初頭から研究が進められてきました。当初は、2Dパッケージングの限界を克服するための手段として開発が始まりました。初期の段階では、技術的な課題が多く、商業化には時間を要しました。しかし、2000年代に入ると、シリコン貫通ビア(TSV)技術の確立とともに、3Dパッケージングの実用化が加速しました。

この期間中、半導体業界はムーアの法則に従って性能向上と小型化を追求してきましたが、2Dパッケージングでは限界が見えてきました。これに対し、3Dパッケージングは、チップを垂直に積み重ねることで、面積効率を高めるとともに、性能向上とコスト削減を両立する手段として注目を集めました。

特に2000年代後半には、メモリチップやプロセッサの3D積層技術が進展し、製品化が進みました。2010年代に入ると、スマートフォンやタブレットなどのモバイルデバイスの高性能化に伴い、3Dパッケージングの需要が急増しました。これにより、技術の標準化や製造プロセスの最適化が進み、市場投入までの時間が短縮されました。

現在、3D半導体パッケージングは、AIや高性能コンピューティング(HPC)、データセンターなどの分野で広く採用されています。特に、データ転送速度の向上とエネルギー効率の改善が求められるアプリケーションにおいて、そのメリットが顕著です。これからも、技術革新が続き、さらなる性能向上とコスト削減が期待されます。

2.5Dパッケージングとの違い

3Dパッケージングと2.5Dパッケージングは、いずれも高密度集積を実現する技術ですが、基本的なアプローチに違いがあります。2.5Dパッケージングでは、複数のチップを単一のインターポーザ上に配置し、水平に接続します。一方、3Dパッケージングでは、チップを垂直に積み重ねて接続します。

2.5Dパッケージングは、製造プロセスが比較的簡単で、既存の製造設備を活用できるため、導入コストが低いという利点があります。また、インターポーザ上でチップ間を接続するため、設計の柔軟性が高く、異なるプロセス技術で製造されたチップを組み合わせることが可能です。これにより、カスタマイズ性が高く、特定の用途に応じた最適化がしやすいです。

一方、3Dパッケージングは、シリコン貫通ビア(TSV)技術を使用してチップ間を垂直に接続するため、データ転送速度が大幅に向上します。これにより、信号遅延が減少し、全体的なシステム性能が向上します。また、3D構造により面積効率が高まるため、デバイスの小型化が可能です。ただし、製造プロセスが複雑であり、導入コストが高いという課題もあります。

2.5Dと3Dの選択は、コスト、性能、設計の柔軟性などの要因によって異なります。一般に、コスト重視の場合は2.5Dが選ばれ、高性能が求められる場合は3Dが選ばれることが多いです。両者は補完関係にあり、具体的なアプリケーションや市場ニーズに応じて使い分けられています。

3Dパッケージングの技術的利点

3D半導体パッケージングには、複数の技術的利点があります。まず、チップ間のデータ転送距離が短縮されるため、信号遅延が大幅に減少します。これにより、全体的なシステム性能が向上し、高速動作が求められるアプリケーションにおいて優れたパフォーマンスを発揮します。

次に、3D構造により面積効率が向上します。複数のチップを垂直に積み重ねることで、基板上の占有面積を削減できるため、デバイスの小型化が可能です。これは、モバイルデバイスやウェアラブルデバイスなど、小型化が求められる製品にとって重要な利点です。また、エネルギー効率の向上も期待できます。チップ間の距離が短いため、消費電力が低減し、バッテリー寿命の延長や省エネルギーが実現します。

さらに、3Dパッケージングは、複数の異なる機能を統合できる柔軟性も持っています。例えば、プロセッサ、メモリ、センサーなどを一つのパッケージ内に統合することで、システム全体の性能向上とコスト削減が図れます。これにより、複雑なシステム設計が簡素化され、開発期間の短縮や製造コストの削減が可能です。

最後に、信頼性の向上も挙げられます。3Dパッケージングは、TSV技術を利用してチップ間を直接接続するため、配線の断線や接触不良のリスクが低減します。これにより、製品の信頼性が向上し、長期間の安定した動作が期待できます。

ビジネスインパクトの概要

3D半導体パッケージングの導入は、さまざまなビジネスに大きなインパクトをもたらしています。まず、デバイスの性能向上と小型化により、製品の競争力が大幅に強化されます。高性能なプロセッサやメモリを使用することで、処理速度やストレージ容量が向上し、消費者のニーズに応える製品が提供可能です。これにより、企業は市場シェアを拡大し、収益を増加させることができます。

また、3Dパッケージングは製造コストの削減にも寄与します。複数のチップを一つのパッケージに統合することで、製造プロセスが簡略化され、材料費や生産時間が削減されます。これにより、企業は製品コストを低減し、価格競争力を高めることができます。また、エネルギー効率の向上により、運用コストも削減され、持続可能なビジネスモデルの構築が可能となります。

さらに、3Dパッケージング技術の進化は、新たなビジネスチャンスを創出します。特に、AIやIoT分野では、高性能でエネルギー効率の良いデバイスが求められており、3Dパッケージング技術はこれらのニーズに応える重要な要素です。これにより、新製品の開発や新市場への参入が促進され、企業の成長が加速します。

総じて、3D半導体パッケージングは、企業の競争力強化、コスト削減、新たなビジネスチャンスの創出など、多方面でビジネスに対するポジティブな影響をもたらします。

産業界での応用例

3D半導体パッケージングは、さまざまな産業分野で応用されています。特に注目されるのは、スマートフォンやタブレットなどのモバイルデバイスです。これらのデバイスは高性能でありながら小型であることが求められ、3Dパッケージング技術によってその要件が満たされています。例えば、最新のスマートフォンでは、プロセッサとメモリが3D構造で統合され、高速なデータ処理と低消費電力が実現されています。

次に、データセンターや高性能コンピューティング(HPC)分野でも3Dパッケージングが活用されています。これらの分野では、膨大なデータ処理能力とエネルギー効率が重要です。3Dパッケージングにより、サーバーやスーパーコンピュータの性能が向上し、より効率的なデータ処理が可能となります。また、エネルギー消費の削減により、運用コストの低減が実現されます。

さらに、3Dパッケージングは、自動車産業においても重要な役割を果たしています。自動運転技術や車載AIシステムには、高度な処理能力が求められます。3Dパッケージングを使用することで、車載デバイスの小型化と高性能化が実現され、安全性と効率性が向上します。これにより、自動車メーカーは先進的な機能を搭載した車両を市場に投入できるようになります。

その他、医療分野でも3Dパッケージング技術は応用されています。医療機器やウェアラブルデバイスは、小型で高性能なセンサーやプロセッサが必要です。3Dパッケージングにより、これらのデバイスが効率的に機能し、患者の健康管理や診断がより正確に行えるようになります。

3Dパッケージングのコスト構造

3D半導体パッケージングのコスト構造は、複数の要素により構成されています。まず、製造プロセスの複雑さがコストに大きな影響を与えます。3Dパッケージングでは、シリコン貫通ビア(TSV)技術を用いるため、従来の2Dパッケージングに比べて高度な製造技術が必要です。これにより、初期投資や設備コストが高くなる傾向があります。

次に、材料費も重要な要素です。3Dパッケージングでは、高品質なシリコンウエハや専用の接続材が必要です。これにより、材料費が増加しますが、製品の性能向上と信頼性向上を考慮すると、その価値は大きいです。また、3Dパッケージングにより、複数のチップを一つのパッケージに統合できるため、最終製品のコスト削減に寄与します。

労働コストも無視できない要素です。高度な技術を持つエンジニアや技術者が必要とされるため、人件費が高くなる可能性があります。しかし、3Dパッケージングの導入により、生産効率が向上し、長期的にはコスト削減が期待できます。

最後に、研究開発費もコスト構造の一部を占めます。3Dパッケージング技術は進化を続けており、最新技術の開発には多額の投資が必要です。企業は競争力を維持するために、継続的な研究開発を行い、新技術の導入を進めています。これにより、初期コストは高くなりますが、将来的な利益を見据えた投資と考えられます。

総じて、3D半導体パッケージングのコスト構造は、製造プロセス、材料費、労働コスト、研究開発費など多岐にわたりますが、技術の進化とともにコスト効率が改善されつつあります。

市場動向と予測

3D半導体パッケージング市場は、急速に成長しています。技術の進化とともに、多くの企業がこの技術を採用し始めており、市場規模は拡大の一途をたどっています。特に、スマートフォンやタブレットなどのモバイルデバイス、データセンター、高性能コンピューティング(HPC)などの分野での需要が高まっています。

調査によると、3Dパッケージング市場は今後数年間でさらに成長すると予測されています。市場規模は年平均成長率(CAGR)で10%以上の成長が見込まれており、2020年代後半には数十億ドル規模に達すると予測されています。この成長は、技術の進歩とともに製品の性能向上が進み、より多くのアプリケーションで3Dパッケージングが採用されることによるものです。

また、地域別に見ると、北米やアジア太平洋地域が市場をリードしています。これらの地域には、大手半導体メーカーやテクノロジー企業が集中しており、技術開発と市場投入が迅速に行われています。特に、台湾や韓国などの半導体製造拠点が重要な役割を果たしています。

さらに、エコシステム全体の進化も市場動向に大きな影響を与えています。半導体メーカー、製造装置メーカー、材料メーカーなどが連携し、技術の標準化や製造プロセスの最適化が進んでいます。これにより、3Dパッケージング技術の普及が加速し、市場成長が促進されています。

総じて、3D半導体パッケージング市場は、技術革新と需要の増加により、今後も大きな成長が期待されます。企業はこの市場動向を注視し、競争力を維持するための戦略を練る必要があります。

技術革新の影響

3D半導体パッケージング技術の革新は、業界全体に多大な影響を与えています。まず、技術的な進歩により、デバイスの性能が飛躍的に向上しました。シリコン貫通ビア(TSV)技術の導入により、チップ間のデータ転送速度が向上し、信号遅延が大幅に減少しました。これにより、プロセッサやメモリの性能が向上し、高速かつ効率的なデータ処理が可能となりました。

次に、3Dパッケージング技術の進化は、製品の小型化と省電力化を推進しました。複数のチップを垂直に積み重ねることで、基板上の占有面積を削減し、デバイスの小型化が実現されました。これにより、モバイルデバイスやウェアラブルデバイスなど、小型化が求められる製品において、性能と機能の両立が可能となりました。また、エネルギー効率が向上し、バッテリー寿命の延長や省エネルギー化が実現されました。

さらに、3Dパッケージング技術の革新は、新たなビジネスチャンスを生み出しました。特に、AIやIoT分野では、高性能でエネルギー効率の良いデバイスが求められており、3Dパッケージング技術はこれらのニーズに応える重要な要素です。これにより、新製品の開発や新市場への参入が促進され、企業の成長が加速しました。

また、技術革新は製造プロセスの効率化にも寄与しています。高度な製造技術により、生産効率が向上し、コスト削減が可能となりました。これにより、企業は競争力を維持しながら、高品質な製品を市場に提供できるようになりました。

エコシステムへの影響

3D半導体パッケージング技術の普及は、エコシステム全体に大きな影響を及ぼしています。まず、半導体メーカー、製造装置メーカー、材料メーカーなど、関連企業間の協力が重要となります。技術の標準化や製造プロセスの最適化が進むことで、業界全体の生産効率が向上し、競争力が強化されます。

次に、3Dパッケージング技術の導入は、サプライチェーン全体に影響を与えます。高度な技術を持つサプライヤーとの連携が必要となり、新たなパートナーシップが形成されます。これにより、品質管理や納期管理が厳格に行われ、製品の信頼性が向上します。また、サプライチェーンの効率化により、コスト削減が可能となり、最終製品の価格競争力が高まります。

さらに、3Dパッケージング技術の進化は、人材育成にも影響を与えます。高度な技術を扱うため、エンジニアや技術者のスキルアップが求められます。企業は専門知識を持つ人材を確保し、継続的な教育やトレーニングを行うことで、技術力の向上を図ります。これにより、企業の技術競争力が強化され、革新的な製品の開発が促進されます。

また、エコシステム全体での環境への影響も考慮されます。3Dパッケージング技術は、省エネルギー化や廃棄物削減に貢献し、持続可能なビジネスモデルの構築を支援します。これにより、企業は環境に優しい製品を提供し、社会的責任を果たすことができます。

挑戦と解決策

3D半導体パッケージング技術の導入には、いくつかの挑戦が伴います。まず、技術的な複雑さが挙げられます。シリコン貫通ビア(TSV)技術の実装には高度な製造技術が必要であり、初期投資や設備コストが高くなります。これに対する解決策として、業界全体での技術標準化やプロセスの最適化が進められています。これにより、製造コストが削減され、技術の普及が加速します。

次に、信頼性の確保も重要な課題です。3Dパッケージングでは、チップ間の接続が複雑であり、品質管理が難しいことがあります。これに対する解決策として、厳格な品質管理プロセスや高度なテスト技術が導入されています。また、サプライチェーン全体での協力により、信頼性の高い材料や部品の供給が確保されます。

さらに、エネルギー効率の向上も課題の一つです。高性能なデバイスを実現するためには、消費電力の削減が必要です。これに対する解決策として、低消費電力の設計技術や省エネルギー材料の使用が進められています。これにより、デバイスのエネルギー効率が向上し、バッテリー寿命の延長や省エネルギー化が実現されます。

最後に、人材育成も重要な課題です。高度な技術を扱うためには、専門知識を持つエンジニアや技術者が必要です。これに対する解決策として、企業は継続的な教育やトレーニングプログラムを実施し、人材のスキルアップを図っています。また、大学や研究機関との連携により、次世代の技術者を育成する取り組みも進められています。

まとめ

3D半導体パッケージング技術は、半導体業界において重要な進展をもたらしています。デバイスの性能向上や小型化、省電力化を実現することで、さまざまな産業分野での応用が進んでいます。ビジネスインパクトも大きく、企業の競争力強化やコスト削減、新たなビジネスチャンスの創出に寄与しています。

技術革新とエコシステム全体の進化により、3Dパッケージング技術は今後もさらなる発展が期待されます。