微細化の限界が叫ばれて久しい半導体業界で、いま最も注目を集めているのが「チップレットアーキテクチャ」です。5nm、3nm、そして2nmへと進む中で設計コストは急騰し、単一ダイによる高性能化は経済合理性を失いつつあります。

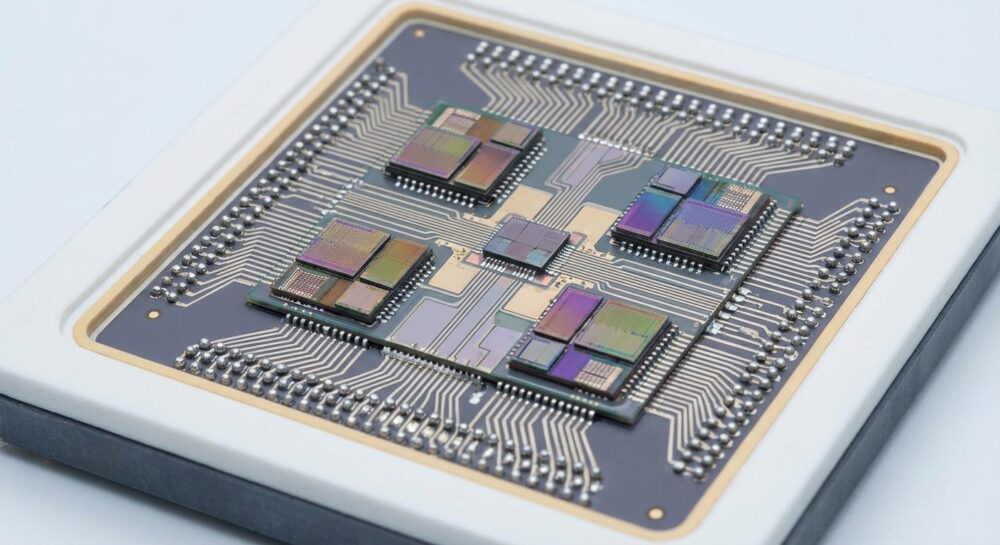

その打開策として急速に普及しているのが、複数の小さなダイを高度なパッケージングで統合するチップレット技術です。世界市場は2025年の約135億ドル規模から翌年には200億ドル超へ拡大し、年平均成長率60%超という異例の成長を遂げています。

AIスーパーコンピュータ、自動運転、AI PC、そして国家戦略にまで波及するこの潮流は、単なる実装技術の進化ではありません。本記事では、UCIe 2.0による標準化、NVIDIAやIntelの最新動向、CoWoSやHBM4の供給制約、日本のRapidusやJOINT3の挑戦までを体系的に整理し、チップレットがもたらす技術・市場・地政学インパクトを立体的に解説します。

ポスト・ムーア時代とチップレット必然論:なぜ単一ダイは限界を迎えたのか

2026年の半導体産業は、いわゆる「ポスト・ムーア時代」の現実に真正面から向き合っています。トランジスタの微細化は5nm、3nm、そして2nm世代へと進みましたが、物理的限界と経済的合理性の乖離が急速に拡大しています。従来の単一ダイ(モノリシック)SoCは、性能向上の象徴である一方で、設計コストと製造リスクの塊にもなりつつあります。

SNS Insiderなどの市場分析によれば、先端ノードにおける設計コストは世代を追うごとに増大し、歩留まりの低下が収益構造を圧迫しています。特にAIやHPC向けの巨大ダイでは、わずかな欠陥がチップ全体の廃棄につながります。ダイ面積が大きいほど欠陥に当たる確率が高まるという、半導体製造の基本法則が、単一ダイの限界を露呈させています。

| 観点 | 単一ダイSoC | チップレット構成 |

|---|---|---|

| 歩留まり | 大面積化で急低下 | 小ダイ分割で改善 |

| 設計コスト | 世代ごとに爆発的増加 | 再利用で抑制可能 |

| 拡張性 | 固定構成 | 用途別に柔軟に構成 |

加えて、単一ダイには「レチクルリミット」という露光装置由来の物理的制約があります。最先端AIプロセッサは、単一ダイでは収まりきらない規模へと肥大化しており、パッケージレベルでの統合なしには成立しません。TechInsightsや各種業界レポートが指摘する通り、先進パッケージングは今や前工程と同等の戦略領域になっています。

経済合理性の観点でも転換点を迎えています。Chiplets市場は2025年の約135億ドル規模から2026年には200億ドル超へと急拡大する予測が示されており、高成長の背景には単一ダイではビジネスが成立しにくくなった現実があります。巨大ダイを1枚作るよりも、機能ごとに分割し、必要な部分だけを先端ノードで製造するほうが投資効率に優れます。

さらに重要なのは、技術進化のスピードです。AIアクセラレータや車載SoCでは、CPU、GPU、NPU、I/Oなどの進化サイクルが異なります。単一ダイでは全機能を同時に刷新する必要がありますが、チップレットなら特定機能だけを世代更新できます。これは単なるコスト問題ではなく、イノベーション速度の問題でもあります。

UCIe 2.0の本格実装が進む2026年現在、異なるベンダーやファウンドリ製チップレットを統合できる環境が整いつつあります。これは、単一ダイという閉じた設計思想から、分業と協調を前提としたエコシステム型設計への構造転換を意味します。

ポスト・ムーア時代とは、微細化が止まる時代ではありません。むしろ、微細化だけに依存しない性能向上モデルへと移行する時代です。単一ダイの限界が明確になった今、チップレットは代替案ではなく、構造的必然として半導体の新常識になりつつあります。

世界市場は年率60%超で拡大:地域別シェアとAI需要の爆発

2026年のチップレット市場は、半導体産業の中でも突出した成長曲線を描いています。2025年の135.5億ドルから2026年には225.8億ドルへと急拡大し、年平均成長率(CAGR)は65.3%に達すると報告されています。GlobeNewswireの市場分析によれば、2030年代前半には1,600億ドル規模に到達する可能性も示唆されており、もはや一過性のブームではありません。

この成長を牽引しているのが生成AIおよび大規模言語モデル向けアクセラレータ需要です。単一ダイではレチクル制限を超える巨大な演算資源を搭載できないため、複数チップレットを高度パッケージで統合する設計が事実上の標準となりました。AI向けGPUやASICの急増が、市場全体の構造を塗り替えています。

地域別に見ると、製造インフラと設計主導権の分業が鮮明です。

| 地域 | 2026年動向 | 特徴 |

|---|---|---|

| アジア太平洋 | 約40%超の最大シェアを維持 | 先端パッケージング・製造基盤が集中 |

| 北米 | 36%超、最速成長(CAGR約18.9%) | AIアクセラレータ設計と標準化主導 |

| 欧州ほか | 拡大基調 | 車載・産業用途で存在感 |

Grand View Researchなどの調査では、アジア太平洋地域が最大市場を維持すると分析されています。TSMCを中心とした先端パッケージ能力の集中が背景にあります。一方で北米は、UCIeなどの標準化推進とAI半導体企業の集積により、設計・アーキテクチャ面で強い影響力を持っています。

用途別では、2026年時点ではCPUが約34%と最大シェアを占めていますが、最も成長が速いのはAI ASIC分野です。AI学習・推論向けに最適化された専用チップレット構成が、HPCやデータセンター投資を押し上げています。

重要なのは、この市場拡大が「微細化競争」ではなく「統合力競争」へ軸足を移している点です。微細化だけでは解決できない性能要求を、複数ダイの統合で乗り越える構造に変わりました。AIモデルの巨大化が続く限り、チップレット需要は構造的に拡大する可能性が高いとIDCやFortune Business Insightsも指摘しています。

結果として、世界市場は単なる数量増ではなく、設計思想そのものの転換によって年率60%超という異例の拡大を遂げています。AI需要の爆発が、地域間の役割分担とサプライチェーン再編を同時に加速させているのが2026年の実像です。

標準化の転換点UCIe 2.0:マルチベンダー時代の幕開け

UCIe 2.0の本格実装が進んだ2026年は、チップレットが「自社完結型技術」から「業界共通インフラ」へと転換した歴史的な年です。

2024年8月に仕様が公開されたUCIe 2.0は、2026年に入り主要ベンダーの製品設計へ本格採用が始まりました。UCIeコンソーシアムの発表によれば、同仕様は物理層から管理機構までを包括的に定義し、単なるインターコネクト規格を超える役割を担っています。

最大の転換点は、異なる企業・異なるファウンドリで製造されたチップレットを同一パッケージで統合できる「マルチベンダー前提」の設計思想が確立されたことです。

従来はAMDやIntelのような単一企業が内部技術として最適化していましたが、UCIe 2.0では設計・検証・管理の共通化が進みました。

特に注目すべきは、UCIe DFx Architecture(UDA)の導入です。これはテストやテレメトリ、デバッグ機構を標準化し、System-in-Package全体の可視性を担保する枠組みです。

これにより、複数社製チップレットを組み合わせた場合でも、品質保証や障害解析を統一的に行えるようになりました。

| 項目 | UCIe 1.x | UCIe 2.0 |

|---|---|---|

| エコシステム | 初期相互接続 | マルチベンダー前提設計 |

| 管理機構 | 限定的 | UDAによる統合管理 |

| パッケージ対応 | 2.5D中心 | 3D積層・ハイブリッドボンディング最適化 |

| 後方互換性 | ― | 1.0/1.1と完全互換 |

また、3Dパッケージングへの最適化も重要です。UCIe 2.0はハイブリッドボンディングを前提とした高密度接続をサポートし、AIやHPCで求められる帯域要求に応えています。仕様上は後方互換性を維持しながらデータレートを拡張しており、既存資産を活かした段階的移行が可能です。

ISSCCでIntelが示した構成可能な2.5Dインターフェース実証は、その象徴的事例です。異なるファウンドリ製チップレットを動的に接続・制御するアーキテクチャは、チップレットを固定的な物理部品から、ソフトウェア制御可能な演算ファブリックへ進化させる方向性を示しました。

この標準化により、CPU、GPU、AIアクセラレータ、I/O、メモリインターフェースを最適な企業から選択する“ミックス・アンド・マッチ”型設計が現実のものとなりました。設計企業は差別化領域に集中でき、製造・後工程企業は接続保証という共通ルールのもとで参入できます。

Fortune Business Insightsなどの市場分析が示す急成長の背景には、単なる需要拡大だけでなく、標準化によって参入障壁が構造的に再定義されたことがあります。2026年は、チップレットが閉じた最適化競争から開かれたエコシステム競争へと移行した、明確な分岐点です。

ISSCCが示した次世代設計思想:構成可能なチップレットと演算ファブリック

2026年のISSCCで明確になったのは、チップレットが単なる分割設計ではなく、ソフトウェアで再構成可能な「演算ファブリック」へと進化しているという事実です。とりわけIntelが発表した構成可能な2.5Dチップレット・インターフェースは、その象徴的な成果といえます。

ISSCCの報告によれば、同社は異なるファウンドリで製造された20種類以上のチップレットを単一のシリコン基板上に統合し、動的にルーティングを切り替えるアーキテクチャを実証しました。これは固定的なSoC構成からの決別を意味します。

ハードウェアを「焼き付ける」時代から、用途に応じて再構成する時代へ──設計思想そのものが転換しています。

従来のモノリシック設計では、機能追加や仕様変更は次世代チップの再設計を待つ必要がありました。しかし構成可能なチップレット設計では、用途ごとに最適な計算ブロックを組み合わせ、不要なブロックはスリープさせることが可能です。

この設計思想を支えているのがUCIe 2.0です。UCIe Consortiumの仕様によれば、データレートの向上だけでなく、DFx Architectureによりテストやテレメトリを標準化し、マルチベンダー環境での信頼性を担保しています。

| 従来SoC | 構成可能チップレット |

|---|---|

| 単一ダイに機能集約 | 機能ごとに分割・最適化 |

| 設計変更は再テープアウト | 構成変更で対応可能 |

| 用途固定型 | 用途別に動的最適化 |

ISSCCで示されたもう一つの重要な視点は、「演算ファブリック」という概念です。これはチップレット間の接続を単なるI/Oではなく、統一された内部ネットワークとして扱う考え方です。

演算資源、メモリ帯域、アクセラレータをファブリック上で抽象化することで、AI推論、HPC、車載制御など異なるワークロードを同一基盤上で効率的に切り替えられます。BerkeleyのAIアーキテクチャ研究でも、エネルギー効率向上には計算と相互接続の協調設計が不可欠と指摘されています。

特に注目すべきは、電力管理との統合です。アクティブなチップレットのみを選択的に駆動し、負荷に応じて帯域を動的制御する設計は、AIワークロードの変動性に極めて適しています。

結果として、2026年のISSCCが示した方向性は明確です。チップレットは物理的な分割技術ではなく、計算資源をサービスとして再構成するためのアーキテクチャ基盤へと昇華しました。設計者の役割も、単一チップを作ることから、最適なファブリックを編成することへと変わりつつあります。

NVIDIA RubinとHBM4統合:AIスーパーコンピュータの新構造

NVIDIAが発表したRubinプラットフォームは、チップレット時代の完成形ともいえる統合アーキテクチャを提示しています。単一GPUの巨大化ではなく、複数の計算ダイと最新世代メモリを高度な先進パッケージで束ね、一つのAIスーパーコンピュータとして機能させる設計思想が中核です。

同社の発表によれば、RubinはVera CPU、Rubin GPU、HBM4、BlueField-4 DPUなど計6チップで構成され、学習と推論を単一基盤で最適化します。とりわけHBM4との物理的・論理的統合が、従来世代との決定的な差を生み出しています。

| 構成要素 | 主な特徴 | 戦略的意義 |

|---|---|---|

| Rubin GPU | TSMC 3nm(N3P)採用、前世代比でAI性能約5倍 | 大規模モデル学習・推論の中核演算 |

| Vera CPU | 88コア(176スレッド)、GPUと広帯域コヒーレント接続 | データ前処理と制御を高速化 |

| HBM4 | 8〜12スタック統合、超高帯域幅 | メモリボトルネックの解消 |

| BlueField-4 DPU | ストレージ・ネットワーク処理統合 | AIエージェント処理の分散最適化 |

HBM4は2048ビット級インターフェースを採用し、従来世代を大きく上回る帯域を実現します。市場分析でも指摘されている通り、2026年時点でHBM4は主要3社の供給分がほぼ完売するほど需要が逼迫しています。これは単なる高速化ではなく、AIモデルの巨大化がメモリ帯域に直結する時代に入ったことを示しています。

RubinではTSMCのCoWoS-L技術を用い、GPUダイとHBM4をシリコンブリッジで接続しています。これにより大面積パッケージ化が可能となり、レチクル制限を超える演算密度を実現しています。金融系メディアの分析でも、NVIDIAがCoWoS容量の大部分を確保していることが指摘されており、設計力と供給確保を同時に押さえる戦略が鮮明です。

特筆すべきは、Rubinが単体GPUではなく「システムとしてのチップレット」である点です。CPUとGPUがコヒーレントに結合され、DPUがデータフローを最適化することで、数兆パラメータ級モデルの推論コストを大幅に削減したと同社は説明しています。

AIスーパーコンピュータの設計思想は、もはや単一ダイの微細化競争ではありません。計算、メモリ、ネットワークをチップレットとして最適配置し、先進パッケージで束ねる統合力こそが競争優位を決定づけます。Rubinはその代表例であり、HBM4との融合は次世代AIインフラの標準像を提示しているのです。

Intel 18AとPanther Lake:AI PCを加速する分離型アーキテクチャ

Intel 18AプロセスとPanther Lakeの組み合わせは、AI PC時代における「分離型アーキテクチャ」の本格実装を象徴しています。従来の単一ダイ設計から脱却し、コンピュートとグラフィックスを物理的に分けたチップレット構成を採用することで、性能・電力効率・拡張性を同時に引き上げています。

Intelの公式発表によれば、Core Ultra Series 3(Panther Lake)は同社初のIntel 18Aノード採用製品です。18AではGate-All-Around(GAA)トランジスタ世代への移行が進み、リーク電流の抑制と高密度化を両立しています。これがAI処理の常時稼働を前提とするPC設計において重要な土台となっています。

| 項目 | Panther Lakeの特徴 |

|---|---|

| 製造プロセス | Intel 18A(最先端ノード) |

| 構造 | コンピュート・ダイとGPUダイの分離型チップレット |

| GPU性能 | 前世代比77%以上向上 |

| AI処理 | NPU単体で高性能、AI PC市場を主導 |

| 電力設計 | Low Power Islandにより長時間駆動 |

特に注目すべきは、**分離型アーキテクチャがもたらす設計自由度の高さ**です。CPU、GPU、NPUといった機能ブロックを個別最適化できるため、歩留まり改善とSKU展開の柔軟性が大きく向上します。ISSCCでIntelが示した構成可能なチップレット接続技術の流れとも整合しており、将来的な機能拡張も視野に入ります。

グラフィックスでは統合型Intel Arcが前世代比77%以上の性能向上を達成しました。Counterpoint ResearchのCES分析でも、AI PCカテゴリーにおいてGPUとNPUの同時強化が競争軸になっていると指摘されています。これは生成AIアプリケーションのローカル実行を前提とした進化です。

さらに、Low Power Island設計によりバックグラウンド処理を超低消費電力領域に隔離し、ノートPCで最大27時間のバッテリー駆動を実現しています。**AIを常時オンにしながら電力を抑えるという相反課題を、物理分離で解決した点が本質的な価値**です。

分離型アーキテクチャは単なる性能向上策ではありません。AIワークロードの増減に応じて最適なダイ構成を設計できるため、エンタープライズ向け高性能モデルから法人モバイル向け省電力モデルまで、同一世代で多層展開が可能になります。Intel 18AとPanther Lakeは、AI PCを「高性能化」するだけでなく、「構成可能なプラットフォーム」へ進化させた転換点といえます。

Apple Mシリーズのモジュール化戦略と2nm世代への布石

Apple Siliconはこれまで「巨大な単一ダイ」で高性能を実現してきた印象が強いですが、2026年時点では設計思想が明確に次の段階へ進んでいます。キーワードはモジュール化です。M5世代以降、CPU・GPU・メディアエンジンなどの機能ブロックを物理的・論理的に分離し、構成を柔軟に最適化するアプローチが本格化しています。

Macworldなどの報道によれば、M5 Pro/Max/Ultraではコア構成のバリエーションがより細分化され、用途に応じたSKU設計が進んでいます。これは単なるラインアップ拡充ではなく、チップレット的発想による製品ポートフォリオ最適化と見るべき動きです。

モジュール化がもたらす設計・事業上の効果

| 観点 | 従来型(単一大型ダイ) | モジュール化設計 |

|---|---|---|

| 歩留まり | 大面積化で低下しやすい | 小ダイ分割で改善余地 |

| SKU展開 | 設計ごとに再設計負担 | ブロック組み合わせで柔軟化 |

| コスト管理 | 先端ノード依存度が高い | 機能別に最適ノード選択が可能 |

特に重要なのは、先端ノードを「全面適用」から「戦略的適用」へと転換できる点です。高性能CPUやGPUのみを最先端プロセスで製造し、I/Oや一部ロジックは成熟ノードを活用することで、コストと供給リスクを抑制できます。これはTSMCの3nm〜2nm世代でキャパシティ制約が続く中、極めて合理的な判断です。

さらに2026年後半に登場が見込まれるM6では、2nmプロセス採用が有力視されています。業界報道では、TSMCの2nmはGAA構造を採用し、電力効率とトランジスタ密度の両立を図るとされています。Appleがこれを早期に取り込む背景には、単なる性能競争以上に、将来世代に向けたモジュール設計との親和性があります。

OLED Macへの最適化も示唆されており、表示制御や電力マネジメントとの統合度が一段と高まる可能性があります。これはSoC単体の性能向上ではなく、デバイス全体のエネルギー設計を再定義する取り組みです。

重要なのは、AppleがUCIeのような外部標準を前面に出す戦略ではなく、垂直統合モデルを維持しながら内部的にモジュール化を進めている点です。つまり、エコシステムは閉じたまま、内部アーキテクチャは分散化するという独自路線です。

この戦略は、2nm以降に予想されるさらなる設計コスト上昇に対する備えでもあります。巨大な単一ダイで限界に挑むのではなく、分割・再構成可能な構造を前提に世代進化を進める。Mシリーズのモジュール化は、ポスト・ムーア時代におけるAppleの持続的競争優位を支える布石と言えます。

CoWoS逼迫とHBM4完売:先進パッケージングが握る覇権

2026年の半導体競争を語るうえで、設計力以上に注目すべきなのが先進パッケージングの供給制約です。とりわけTSMCのCoWoSと、次世代メモリHBM4の需給逼迫は、AIチップ市場の成長速度そのものを左右しています。

業界関係者の間では「設計はできても、パッケージできない」という言葉が現実味を帯びています。実際、複数の市場分析や企業コメントによれば、2026年分の主要キャパシティはほぼ埋まっている状況です。

| 項目 | 2026年の状況 | 示唆 |

|---|---|---|

| CoWoS需要 | 年間約100万ウェハ規模(2024年比で急増) | AI向け需要が爆発的に拡大 |

| NVIDIAの利用比率 | 全体の約60%を占有 | 特定顧客への集中 |

| TSMC生産能力 | 月産8〜10万ウェハ目標 | 増強中も逼迫継続 |

| HBM4供給 | 主要3社とも2026年分ほぼ完売 | メモリがボトルネック |

TSMCのC.C. Wei氏がCoWoS能力は「完全に完売」と強調している通り、供給は極めてタイトです。とりわけAIアクセラレータ向けのCoWoS-Lは、大面積SiPを可能にする一方で、製造難易度も高く、短期間での増産が難しいという構造的制約を抱えています。

さらに深刻なのがHBM4です。2048ビットの広帯域インターフェースを採用するHBM4は、ハイブリッドボンディング(SoIC)による超微細接合が前提となります。銅同士を直接接合するこの方式は、ナノレベルの平坦化と清浄度を要求し、歩留まり確保が容易ではありません。

実際、NVIDIAの次世代プラットフォームではHBM4を8〜12スタック統合する構成が採られていますが、これは単なる性能向上ではなく、巨大モデル時代の帯域要求に応えるための必然です。しかしHBM4が完売状態である以上、出荷台数そのものが物理的に制約されます。

FinancialContentの分析でも指摘されているように、2026年のAI経済を制する「キングメーカー」は設計企業ではなく先進パッケージング能力です。CoWoS-SからCoWoS-Lへの移行、大面積化、そしてHBM4統合技術――これらを同時に実装できる企業は限られています。

その結果、AI半導体の覇権は演算アーキテクチャの優劣だけでなく、後工程を含めた垂直統合的な供給確保力によって決まる時代に入りました。2026年は、パッケージングが戦略資産へと格上げされた転換点として記憶される年になりそうです。

ハイブリッドボンディングと3D積層:製造難易度の新次元

ハイブリッドボンディングと3D積層は、2026年のチップレット時代において製造難易度を一段と引き上げる中核技術です。特にHBM4の統合が本格化したことで、従来のはんだバンプ接続では対応できない超高密度・超広帯域の実装が求められています。

HBM4は2048ビットの広帯域インターフェースを採用しており、ロジックダイとの接続には銅と銅を直接結合するハイブリッドボンディングが事実上不可欠です。FinancialContentの分析によれば、この技術こそが2026年のAI半導体競争の“キングメーカー”になっていると指摘されています。

両者の違いを整理すると、製造難易度の質的変化が見えてきます。

| 項目 | 従来バンプ接続 | ハイブリッドボンディング |

|---|---|---|

| 接続方式 | はんだバンプ | 銅-銅直接接合 |

| ピッチ | 数十µm級 | 10µm未満級 |

| 電気特性 | 抵抗・寄生成分が相対的に大きい | 低抵抗・低遅延 |

| 製造要件 | 高精度実装 | ナノレベル平坦化・極限清浄度 |

最大の壁は、ウェハ表面の平坦度と清浄度です。銅同士を直接接合するため、CMPによる原子レベルの平坦化と、微粒子混入を極限まで排除するクリーン環境が求められます。わずかなパーティクルでも接合不良につながり、大面積SiPでは歩留まりに直結します。

さらに3D積層では、ウェハの反り(ワーページ)制御が極めて重要です。TSMCのSoICやCoWoS-Lの進展により大面積化が進む一方、複数ダイを重ねることで内部応力が複雑化し、熱サイクル時の信頼性設計が難しくなっています。TechInsightsの2026年レポートでも、先進パッケージの歩留まり改善が業界共通課題であると分析されています。

電気的メリットは明確です。接続長が短縮されることで消費電力とレイテンシが低減し、AIワークロードに不可欠なメモリ帯域を効率的に活用できます。しかしその裏側では、装置投資、材料開発、プロセス統合の三位一体の高度化が進んでいます。

ハイブリッドボンディングと3D積層は、設計自由度を飛躍的に高める一方で、製造を“ナノ精度の総力戦”へと変えました。 2026年現在、この技術を安定量産できる企業は限られており、それ自体が競争優位の源泉となっています。

日本の戦略転換:RapidusとLSTCが描く設計・製造一体モデル

日本の半導体戦略は2026年、明確な転換点を迎えています。鍵となるのが、RapidusとLSTCが推進する設計と製造を一体化したチップレット前提のモデルです。

これは従来の「製造受託」中心でも、「設計専業」でもありません。2nm世代の前工程から先進パッケージングまでを統合し、設計段階からパッケージを含めた最適化を行う垂直横断型のアプローチです。

RapidusとLSTCの役割分担

| 主体 | 主な機能 | 戦略的意義 |

|---|---|---|

| Rapidus | 2nm GAAプロセス製造、チップレット試作ライン(IIM-1) | 前後工程の一体提供による最適化 |

| LSTC | 2nm世代設計基盤、RISC-V/AIチップレット開発 | 国産設計エコシステムの中核形成 |

Rapidusは北海道千歳市のIIM-1工場で、2026年春にチップレット対応パイロットラインを稼働予定と公表しています。Tom’s Hardwareによれば、同社は2027年量産を見据え単枚処理を採用し、先端ノードでの歩留まり確保を重視しています。

重要なのは、2nmロジック製造と先進パッケージを分断しない点です。チップレット時代では、トランジスタ性能だけでなく、接続密度や熱設計を含めた「システム最適」が競争力を決めます。

LSTCは設計面の司令塔です。Tenstorrentとの提携により、RISC-V CPUチップレットとAIアクセラレータを組み合わせる2nmエッジAI基盤の開発を進めています。HPCwireの報道でも、この協業は日本におけるオープンチップレット戦略の象徴と位置づけられています。

ここで注目すべきは、IDM型の完全自前主義ではなく、オープン標準とチップレットを前提とした水平分業の高度化を目指している点です。UCIeを視野に入れた設計思想は、将来的なマルチベンダー統合を可能にします。

DeloitteやIDCの分析でも、地政学リスク下では前後工程の分断が供給網の脆弱性を高めると指摘されています。RapidusとLSTCの一体モデルは、単なる技術挑戦ではなく、技術的主権とサプライチェーン強靭化を同時に狙う国家戦略といえます。

チップレットが「計算の新しい言語」となる時代において、日本は製造装置や材料の強みだけでなく、設計思想そのものを再構築しようとしています。その成否は、2nm量産とエコシステム形成の両立にかかっています。

JOINT3コンソーシアムとパネルレベル実装:後工程からの逆襲

チップレット時代において、日本が最も強みを発揮しているのは前工程ではなく後工程です。その象徴が、レゾナック主導のJOINT3コンソーシアムと、パネルレベル実装(PLP)への本格的なシフトです。

2026年、半導体競争の主戦場は微細化ノードだけでなく、いかに大面積・高密度のパッケージを安定かつ低コストで量産できるかへと移っています。JOINT3はまさにこの課題に対する、日本発の構造的回答です。

| 項目 | 従来ウェハ方式 | パネルレベル実装(PLP) |

|---|---|---|

| 基板形状 | 円形(300mm) | 大型長方形パネル |

| 処理チップ数 | 限定的 | 大幅増加 |

| 面積効率 | 周辺ロスあり | 高効率 |

| 主用途 | 標準SiP | HPC/大面積AIパッケージ |

Business Wireによれば、JOINT3には27社のグローバルリーダーが参画しています。材料、装置、検査、実装までを横断的に結びつける体制は、単一企業では到達できない統合力を生み出しています。

特に重要なのが、有機インターポーザを前提とした次世代パッケージ基盤の確立です。シリコンインターポーザに依存する従来型CoWoSに対し、有機材料を活用することでコストと大面積化の両立を狙います。

東京エレクトロンは先端ボンディングや塗布技術を強化し、ディスコは最大400×400mm級パネル対応のダイシング装置を展開しています。アドバンテストはチップレット間高速通信の検証環境を整備し、JX金属は高純度材料供給で支えます。

TrendForceも指摘するように、先端パッケージ装置市場は急拡大しており、後工程はもはや補助的存在ではありません。設計自由度、電力効率、熱管理、歩留まりすべてがパッケージ段階で決まる時代です。

さらに茨城県結城市で稼働するプロトタイプラインは、材料から装置条件までを実証ベースで最適化する場として機能しています。顧客は量産前に検証データを取得でき、設計段階から後工程と並走するモデルが構築されています。

微細化競争で主導権を握れなかった日本が、材料・装置・統合力で逆転を狙う構図です。チップレットが「分割と統合」の思想であるならば、JOINT3はその統合部分を世界標準に押し上げる試みです。

2026年、日本の後工程は単なるサプライヤーではなく、グローバルAI基盤を支配するレバーへと変貌しつつあります。

車載チップレットとSDV:ルネサスR-Car X5Hの拡張性

ソフトウェア定義車両(SDV)の実現に向けて、車載SoCは「固定性能」から「拡張可能な計算基盤」へと進化しています。その象徴が、ルネサスのR-Car X5Hです。3nmプロセスを採用した本製品は、単なる高性能化ではなく、チップレット前提のアーキテクチャによって長期的な機能拡張を可能にしています。

ルネサスの発表によれば、R-Car Gen 5世代はUCIeインターフェースを活用し、外部AIアクセラレータやGPUチップレットを接続できる設計思想を採っています。これにより、車種やグレードごとに異なる演算需要へ柔軟に対応できます。

同一のソフトウェア資産を維持したまま、ハードウェア性能を段階的にスケールできる点が最大の競争優位です。

具体的な拡張性のポイントは以下の通りです。

| 項目 | R-Car X5Hの特徴 | SDVへの意味 |

|---|---|---|

| プロセス技術 | 3nm採用 | 電力効率向上と高集積化 |

| インターコネクト | UCIe対応 | マルチベンダー拡張 |

| Mixed Criticality | 機能分離実装 | 安全性と娯楽の両立 |

特に重要なのが「Mixed Criticality」の実装です。ブレーキやステアリングなどASIL-D相当の安全系機能と、インフォテインメントやAIアシスタントといった非安全系機能を、異なるチップレットで物理的に分離します。これにより、Freedom from Interferenceをハードウェアレベルで担保しつつ、演算資源の効率活用を実現します。

また、3nm世代への移行によって、5nm世代比で30〜35%の消費電力削減が示されています。冷却制約が厳しい車載環境では、この差は航続距離や筐体設計に直結します。電動車両の普及が進む中、半導体の電力効率は車両全体のエネルギー戦略そのものです。

さらに、UCIe準拠という選択はエコシステム戦略でもあります。UCIeコンソーシアムの仕様によれば、異なるベンダー間でのチップレット相互接続が標準化されつつあります。これは将来的に、OEMやTier1が用途特化型AIチップレットを追加実装する余地を意味します。

車両出荷後の機能拡張やサブスクリプション型機能追加を、ハードウェアレベルで支える設計が現実味を帯びてきました。SDVはソフトウェアだけで完結する概念ではなく、拡張可能な半導体アーキテクチャと不可分です。

R-Car X5Hは、単一SoCの性能競争から脱却し、モジュール化された車載コンピューティング基盤へ移行する転換点を示しています。車載チップレットは、性能の問題ではなく「進化し続けられる車」を実現するための構造改革なのです。

シリコンフォトニクスと光I/O:電気配線の限界を超える

チップレットの高密度化が進む2026年、次に立ちはだかっているのが「電気配線の物理的限界」です。トランジスタは微細化できても、チップレット間をつなぐ銅配線は距離が伸びるほど信号減衰と消費電力が急増し、発熱も無視できなくなります。AIやHPC向けパッケージでは、帯域幅の拡大がそのまま電力効率の悪化につながるというジレンマが顕在化しています。

この壁を突破する鍵として注目されているのが、シリコンフォトニクスと光I/Oチップレットです。OFCやIEEE CICCの技術セッションでも議論されている通り、電気信号を光信号へ変換し、パッケージ内外を光で接続するアーキテクチャが実装段階に入りつつあります。

| 項目 | 電気I/O | 光I/O |

|---|---|---|

| 長距離伝送時の損失 | 距離に比例して増大 | 極めて低い |

| 消費電力 | 帯域幅増大で急増 | 同帯域で大幅削減可能 |

| 到達帯域 | 数百Gbps級で制約 | テラビット級に拡張可能 |

Co-Packaged Optics(CPO)はその代表例です。スイッチASICやAIアクセラレータのすぐ隣に光エンジンを配置し、電気配線を最短化することで、従来比で電力消費を大幅に抑えながらテラビット級の帯域を実現します。TechInsightsの2026年先進パッケージングレポートでも、データセンター向けハイエンド機での実用化が進んでいると指摘されています。

Ayar Labsなどの企業は、プロセッサに直接統合可能な光学I/Oチップレットを開発しています。これにより、演算チップレットとメモリ、さらにはラック間接続までを光でシームレスにつなぐ構想が現実味を帯びています。電力を抑えながら帯域を拡張できることは、分散型AIクラスタの経済合理性を根本から変える可能性があります。

もっとも、光化は万能ではありません。レーザー源の安定供給、パッケージ内の熱設計、フォトニクスとCMOSの混載歩留まりなど、製造上の難易度は高いです。ResearchGateで公開されたCPO向け高熱伝導アンダーフィルの研究では、ダイヤモンドフィラーを活用することで放熱性能を大幅に改善できると報告されています。

電気配線の制約から解き放たれることで、チップレットは同一パッケージ内に閉じず、ラック全体を一つの論理的プロセッサとして再構成する道が開けます。2026年は、シリコンフォトニクスが研究テーマから設計選択肢へと格上げされた転換点と言えるでしょう。

極限の熱管理とダイヤモンド材料:高密度3D実装の壁

3D積層とチップレットの高密度化が進む2026年、最大のボトルネックは演算性能ではなく熱です。HBM4を8〜12スタック統合し、3nm世代のロジックをCoWoS-Lで接続する構成では、単位面積あたりの発熱密度が急激に上昇します。電力効率が改善しても、絶対的な消費電力は増大しており、放熱設計はパッケージ全体のアーキテクチャ課題へと格上げされています。

特に3D実装では、上層チップの熱が下層に滞留する「サーマルスタッキング」が深刻です。IEEE CICCやOFC関連の技術資料でも、光I/OやCPO統合時における温度上昇が信頼性へ直結することが指摘されています。温度10℃の上昇が寿命を半減させるというアレニウス則の経験則は、依然として設計現場の前提です。

その中で注目されているのが、ダイヤモンド材料の活用です。ダイヤモンドは理論上2000W/mK級という極めて高い熱伝導率を持ち、銅(約400W/mK)やシリカフィラー充填樹脂を大きく上回ります。2026年に公開されたシリコンフォトニクス向けアンダーフィル研究では、ダイヤモンドフィラーを高充填した材料が従来比で顕著な温度低減効果を示したと報告されています。

| 材料 | 代表的熱伝導率(W/mK) | 用途例 |

|---|---|---|

| シリカ充填樹脂 | 数〜10台 | 従来アンダーフィル |

| 銅 | 約400 | ヒートスプレッダ |

| ダイヤモンド | 1000〜2000級(理論値) | 高熱伝導フィラー、ヒートシンク |

ダイヤモンドフィラーは、ハイブリッドボンディングによる微細接合部周辺のホットスポット緩和にも有効です。バンプピッチが数µm未満へ縮小するなか、局所的な発熱をいかに均一化するかが信頼性の鍵となります。熱応力を低減できれば、ワーページ抑制や接合信頼性向上にも波及効果があります。

さらに、液冷との組み合わせも現実解として広がっています。TechInsightsの2026年アウトルックによれば、HPC向けではパッケージ背面への直接液冷やマイクロチャネル冷却が本格導入段階に入りました。ダイヤモンド系材料で熱を迅速に拡散し、液冷で系外へ排出する二段構えが主流になりつつあります。

ただし課題もあります。ダイヤモンド粉末の均一分散、界面接着性、コスト、量産時の歩留まり確保は依然として高いハードルです。ナノレベルの清浄度が求められるハイブリッドボンディング工程との整合も不可欠です。

高密度3D実装の壁は、もはやトランジスタの微細化ではなく、熱という物理法則そのものです。ダイヤモンド材料はその突破口の一つですが、材料科学、流体設計、パッケージ構造を統合した総合力こそが、次世代AIチップの持続的進化を左右します。

Known Good DieとAI解析:テスト戦略のパラダイムシフト

チップレット時代において、品質保証はもはや最終工程の確認作業ではありません。パッケージング前に「良品であることを証明する」Known Good Die(KGD)戦略が、事業収益を左右する経営課題へと格上げされています。

背景にあるのは、先進パッケージのコスト構造です。FinancialContentの分析によれば、最新世代のAI GPUは1基あたり4万ドル規模に達します。このような高付加価値製品で、1つのチップレット不良により全体が廃棄となるリスクは、従来のモノリシック設計とは比較になりません。

そのため2026年のテスト戦略は、「後工程での検出」から「前工程での予防」へと明確にシフトしています。

| 観点 | 従来SoC | チップレット(2026年) |

|---|---|---|

| 不良発見のタイミング | パッケージ後中心 | ダイ単位で事前保証(KGD) |

| 損失インパクト | 単一チップ単位 | 高価なSiP全体に波及 |

| データ活用 | ロット単位解析 | リアルタイムAI解析 |

Advantestの2026年方針によれば、KGD徹底のためには微細バンプやハイブリッドボンディング対応の高精度プローブ技術が不可欠です。バンプピッチが極小化する中、従来の接触方式では測定誤差やダメージリスクが増大するため、装置・治具レベルでの革新が進んでいます。

さらに注目すべきは、AIによるテストデータ解析の本格実装です。Synopsysとの協業事例が示すように、ウエハ工程から最終テストまでの膨大なデータを統合し、不良の相関パターンを機械学習で抽出するアプローチが実用段階に入りました。

これにより、単なる不良品の選別ではなく、歩留まり低下の予兆検知やプロセス条件の最適化がリアルタイムで可能になります。ビッグデータ解析は、テスト工程をコストセンターから価値創出部門へと変貌させつつあります。

また、システムレベルテスト(SLT)の重要性も増しています。UCIeベースのマルチベンダー構成では、個々のチップレットが良品でも、相互接続やプロトコル階層で不具合が発生する可能性があります。ISSCCや業界報告でも、協調動作検証の高度化が強調されています。

2026年の競争軸は、微細化ノードだけではありません。どれだけ精緻に「良品」を定義し、データで保証できるかが、AI時代の半導体企業の信頼性と収益性を決定づけています。テスト戦略は今や補助工程ではなく、チップレット経済圏の中核インフラとなっています。

地政学リスクとサプライチェーン再編:チップレットが変える勢力図

2026年の半導体産業は、技術競争であると同時に、明確な地政学リスクの最前線でもあります。とりわけチップレットの普及は、従来の「最先端ノードを握る国が覇権を握る」という単純な構図を揺さぶり、サプライチェーンの勢力図を再定義し始めています。

IDCやDeloitteの分析によれば、米中対立は依然として先端露光装置や3nm以下のロジック製造を巡る制限を中心に展開しています。一方で、チップレットは設計と後工程の高度化によって性能を積み上げるアプローチを可能にし、国家戦略に新たな選択肢を与えています。

実際、中国は7nmや14nm世代で製造したダイを複数統合し、先端製品に近い性能を実現する戦略を強化しています。これは露光装置の輸出規制を受ける中での現実的な対応策であり、設計・後工程重視型へのシフトを象徴しています。

一方、先進パッケージング能力の集中は新たなリスクも生み出しています。とりわけTSMCのCoWoSは2026年においても供給が逼迫しており、報道ベースでは年間約100万ウェハ規模の需要に対し能力拡張が追いつかない状況が指摘されています。

| 領域 | 地政学上の意味 | 主なプレーヤー |

|---|---|---|

| 先端ロジック(3nm/2nm) | 輸出規制の中心、技術覇権の象徴 | 米国・台湾・韓国 |

| 先進パッケージング(CoWoS等) | AI性能を左右する実質的ボトルネック | 台湾・日本・一部東南アジア |

| 成熟ノード+統合 | 制裁回避型の性能向上手段 | 中国 |

この構図から見えてくるのは、競争軸が「ナノメートル」から「統合能力」へと拡張しているという事実です。UCIe 2.0の標準化により、異なる国・企業で製造されたチップレットを接続できる環境が整い、サプライチェーンは垂直統合から水平分業へと加速しています。

その結果、台湾依存のリスクを軽減するため、日本や欧州、インド、マレーシアなどが後工程拠点として台頭しています。特に日本ではRapidusやJOINT3コンソーシアムが前工程と後工程を一体で再構築する動きを見せており、技術的主権の確立を国家戦略として推進しています。

チップレットは単なる設計手法ではなく、地政学リスクを分散させるアーキテクチャでもあります。製造、パッケージング、テストを複数地域に分散できるため、単一拠点の停止が即座に全体停止につながる構造からの脱却が可能になります。

もっとも、標準化が進むほど、インターコネクト仕様や検証基盤を握る企業・国の影響力は増大します。標準を制する者がエコシステムを制するという構図は、かつての通信規格やOS競争と同様です。

2026年のサプライチェーン再編は、単なる生産移転ではありません。チップレットを軸に、設計・材料・装置・後工程が再編されることで、半導体の勢力図そのものが再定義されつつあります。国家間競争は続きますが、その舞台はもはや露光装置だけではないのです。

参考文献

- SNS Insider:Chiplet Market Size, Share, Trends & Growth Report, 2033

- GlobeNewswire:Chiplets Market Analysis and Forecast 2026-2030 & 2035

- UCIe Consortium:Press Releases

- NVIDIA Newsroom:NVIDIA Kicks Off the Next Generation of AI With Rubin — Six New Chips, One Incredible AI Supercomputer

- Intel Newsroom:CES 2026: Intel Core Ultra Series 3 Debuts as First Built on Intel 18A

- Business Wire:Resonac Launches 27-Member “JOINT3” Consortium to Develop Next-Generation Semiconductor Packaging

- Renesas Electronics:Renesas Fast-Tracks SDV Innovation with R-Car Gen 5 SoC-Based End-to-End Multi-Domain Solution Platform

- Deloitte:New technologies and familiar challenges could make semiconductor supply chains more fragile