AIの進化が加速するなか、「演算性能」ではなく「メモリ帯域」がボトルネックになる時代に入りました。GPUの性能向上だけでは大規模言語モデルやエージェント型AIの要求を満たせず、高帯域幅メモリ(HBM)がAIインフラの成否を左右しています。

HBM市場は今、かつてないスーパーサイクルの只中にあります。SKハイニックス、サムスン電子、マイクロンの三強体制に変化の兆しが見え、HBM4の量産、2048ビット化、16層積層、さらにはロジック統合といった技術革新が競争軸を塗り替えています。

さらに注目すべきは、日本企業が材料・装置・検査の各分野で不可欠な役割を担っている点です。本記事では、市場データや各社の戦略、次世代GPU「Rubin」との関係、地政学リスクまでを横断し、AI時代におけるHBMの本質とビジネス機会を多角的に整理します。

AI時代に顕在化した「メモリの壁」とHBMの戦略的重要性

AIコンピューティングが急拡大する2026年、半導体業界で最も深刻な課題として顕在化しているのが「メモリの壁」です。GPUやAIアクセラレータの演算性能が指数関数的に向上する一方で、データを供給するメモリ帯域が追いつかず、プロセッサが待ち状態に陥る現象が顕在化しています。

特に大規模言語モデルや生成AIの学習・推論では、数千億〜数兆パラメータ規模の重みを絶えず読み書きする必要があり、演算能力よりもメモリアクセスがボトルネックになるケースが増えています。TechInsightsの2026年メモリ展望でも、AIシステム全体の性能制約要因が「演算」から「データ移動」へ移行していると指摘されています。

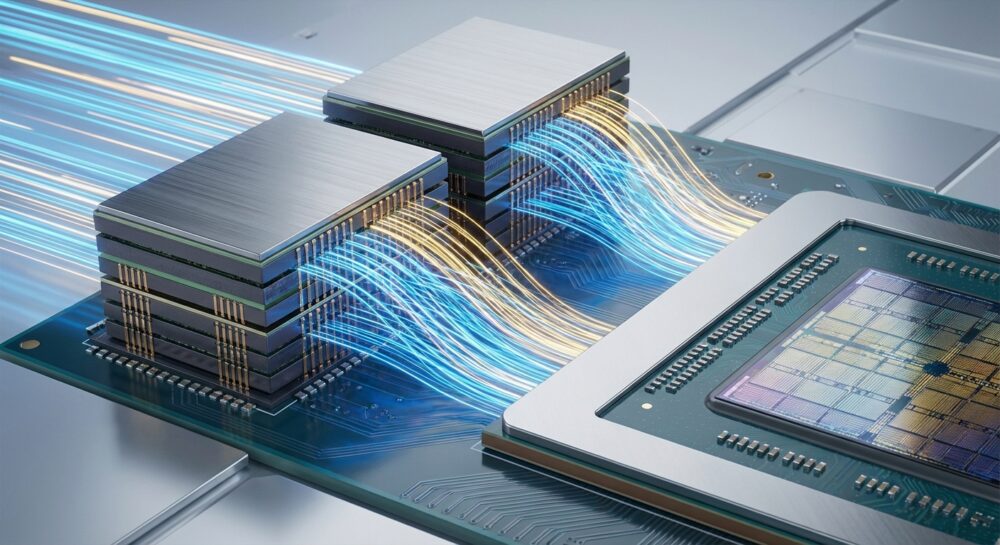

この構造的課題に対する最有力解が、高帯域幅メモリ(HBM)です。従来のDDRやGDDRが基板上で横方向に配置されるのに対し、HBMはDRAMを垂直に積層し、シリコン貫通電極(TSV)で接続する3D構造を採用しています。これにより、極めて広いインターフェース幅を実現し、消費電力あたりのデータ転送効率を大幅に高めています。

| 項目 | 従来型メモリ | HBM4世代 |

|---|---|---|

| 接続方式 | 基板配線(2D) | 3D積層+TSV |

| インターフェース幅 | 数百bit規模 | 2048bit |

| スタック帯域幅 | 数百GB/s級 | 2TB/s級 |

| 電力効率 | 周波数依存で増大 | 低周波・広帯域で効率向上 |

2026年に主流化するHBM4では、インターフェース幅が2048ビットへ倍増し、1スタックあたり最大2TB/s超の帯域幅が可能になりました。EE Timesの報道によれば、これによりAI学習時間を40%以上短縮できるケースも示されています。単なる速度向上ではなく、システム全体のスループットを引き上げる点に本質があります。

さらに重要なのは電力効率です。データセンターでは電力供給と冷却能力が制約条件となっています。HBMは広帯域を低い動作周波数で実現できるため、ビットあたりのエネルギー消費を抑制できます。これはWSTSが予測するメモリ市場30%成長の背景にもある、AIインフラ投資の持続可能性を支える技術的前提です。

ゴールドマン・サックスの分析では、カスタムAIチップ向けHBM需要が前年比82%増とされ、市場全体の3分の1を占める規模に拡大しています。これはHBMが単なる高級メモリではなく、AIアクセラレータの設計思想そのものを規定する戦略資源になったことを意味します。

演算性能がいくら向上しても、メモリが追いつかなければAIは真価を発揮できません。2026年の半導体競争は、プロセッサ開発競争であると同時に、いかに「メモリの壁」を突破するかという構造的競争でもあります。その中心に位置するHBMは、AI時代のインフラを左右する戦略的コンポーネントとして、かつてない重要性を帯びています。

拡大するHBM市場規模とメモリ・スーパーサイクルの実像

2026年のHBM市場は、AIインフラ投資の加速を背景に、かつてない規模で拡大しています。世界半導体市場統計(WSTS)によれば、2026年の世界半導体市場は前年比25%増の約9,750億ドルに達し、そのうちメモリ分野は30%成長が見込まれています。中でもHBM市場は前年比58%増の約546億ドル規模へと急拡大する予測です。

この成長は循環的な回復ではなく、AIという構造要因に支えられた「メモリ・スーパーサイクル」と位置付けられます。従来のPCやスマートフォン需要とは異なり、生成AIや大規模言語モデルの学習・推論基盤が継続的な設備投資を生み出している点が本質的な違いです。

市場構造を見ると、SKハイニックス、サムスン電子、マイクロンの3社による寡占体制が続いています。2025年第2四半期時点ではSKハイニックスが62%と圧倒的首位に立ち、マイクロン21%、サムスン17%が続きました。一方、Design And Reuseなどの報道によれば、2026年はサムスンがHBM4供給を本格化させ、シェア30%超まで拡大する見通しです。

| ベンダー | 2025年Q2シェア | 2026年見通し |

|---|---|---|

| SKハイニックス | 62% | 50%以上維持 |

| サムスン電子 | 17% | 30%以上へ拡大 |

| マイクロン | 21% | 20〜25%で安定 |

特筆すべきは需要の質的変化です。ゴールドマン・サックスの分析では、カスタムASIC向けHBM需要は前年比82%増とされ、市場全体の約3分の1を占める水準に拡大しています。ハイパースケーラー各社が自社設計チップへ移行する中で、HBMはGPU依存から脱却し、より広範なAIアクセラレータの共通基盤となりつつあります。

さらに、マイクロンは2026年までのHBM生産能力が完売済みであると公表しています。供給が需要に追いつかない状況は価格の下支え要因となり、従来のメモリ市況に見られた急激な価格崩落とは異なる局面を形成しています。

今回のスーパーサイクルの実像は「数量拡大」だけでなく、「付加価値の集中」にあります。 HBMは1スタックあたり数十GBという大容量とテラバイト級帯域を備え、AIサーバー1台あたりの搭載数量も増加しています。その結果、システム全体の中でメモリが占めるコスト比率が上昇し、メモリメーカーの収益構造も質的に変化しています。

2026年は、HBM3Eが利益を生み出しつつ、HBM4への移行が本格化する転換点です。AI投資が続く限り、このスーパーサイクルは単なる景気回復局面ではなく、構造的成長フェーズとして認識すべき段階に入っています。

SKハイニックス・サムスン・マイクロン三強のシェア攻防と供給戦略

2026年のHBM市場は、SKハイニックス、サムスン電子、マイクロンの三強による寡占構造が続いていますが、その内実は静的ではありません。出荷量ベースで見ると、2025年第2四半期時点でSKハイニックスが62%と圧倒的首位に立ち、マイクロンが21%、サムスンが17%で続きました。

しかし2026年に入り、HBM4の立ち上がりと主要顧客の認証進展を背景に、サムスンのシェアは30%超へ拡大するとの予測も出ています。市場は単なる数量競争ではなく、世代移行と供給能力の確保を軸とした戦略戦に移行しています。

| 企業 | 2025年Q2シェア | 2026年の戦略焦点 |

|---|---|---|

| SKハイニックス | 62% | NVIDIA向け安定供給、HBM3E/4の両立 |

| サムスン電子 | 17% | HBM4本格参入、1c nm活用 |

| マイクロン | 21% | 高効率設計、米系顧客との連携強化 |

SKハイニックスの強みは、NVIDIA次世代GPU「Rubin」向け主要サプライヤーとしての地位です。EE Timesなどの報道によれば、HBM3EからHBM4への移行期においても安定供給できる体制を構築しており、量産実績と歩留まりの高さが信頼を生んでいます。

一方、サムスンは第6世代10ナノメートル級(1c nm)DRAMを先行投入し、自社ファウンドリとの垂直統合を武器に巻き返しを図っています。HBM4での認証通過が進めば、ロジックからメモリまで一貫提供できる体制は大手顧客にとって大きな魅力になります。

マイクロンは規模では劣るものの、電力効率で差別化しています。同社発表によればHBM3Eで競合比約30%低消費電力を実現し、2026年分のHBM生産能力は既に完売しています。エネルギー効率を重視するハイパースケーラーに深く入り込む戦略が奏功しています。

TrendForceの分析では、HBM4は仕様調整や顧客側の戦略変更の影響で量産時期が慎重に管理されていると指摘されています。つまり、単に技術開発が早い企業が勝つのではなく、顧客のロードマップと歩調を合わせたキャパシティ配分が決定的になります。

さらに、HBM市場は2026年に前年比50%超の成長が見込まれ、メモリ全体の中でも突出した拡大を示しています。供給が逼迫する中で、各社は長期契約や事前予約を通じて需要を囲い込み、価格決定力を高めています。

2026年の三強の攻防は、技術優位性と同時に、戦略的アライアンスと供給網構築力の競争です。HBM4という新世代メモリを巡るこの主導権争いは、AIインフラの勢力図そのものを左右する段階に入っています。

HBM4の技術革新:2048ビット化と2TB/s級帯域のインパクト

HBM4の最大の技術革新は、メモリインターフェースを従来の1024ビットから2048ビットへと倍増させた点にあります。これは単なる数値上の進化ではなく、AIコンピューティングにおける「メモリの壁」を構造的に打ち破るアーキテクチャ転換です。

バス幅を倍に広げることで、動作周波数を過度に引き上げることなく帯域幅を飛躍的に拡大できます。結果として、性能向上と電力効率改善を同時に実現する設計思想へと進化しました。

EE TimesやSemiconductor Engineeringの報道によれば、主要ベンダーは11.0〜11.7Gbps級のピン速度を目標としつつ、スタックあたり2.0〜2.2TB/sという桁違いの帯域を実現し始めています。

| 項目 | HBM3E | HBM4 |

|---|---|---|

| バス幅 | 1024-bit | 2048-bit |

| ピン速度 | 最大9.6Gbps | 11.0〜11.7Gbps |

| スタック帯域 | 約1.2TB/s | 2.0〜2.2TB/s |

この2TB/s級帯域は、GPUやAIアクセラレータの演算ユニットを「待たせない」ための基盤です。メモリ帯域が不足すると、いかに演算性能が高くても実効性能は頭打ちになりますが、HBM4ではその制約が大きく緩和されます。

特に大規模言語モデルの学習では、重みパラメータやアクティベーションの読み書きがボトルネックになります。複数スタックを組み合わせた場合、総帯域は10TB/sを超える構成も現実的になり、学習時間を40%以上短縮できるとの分析も報告されています。

さらに重要なのは、広帯域化が電力効率に直結している点です。広いバス幅を比較的低いクロックで駆動することで、ビットあたりのエネルギー消費を抑制できます。データセンター全体の電力制約が深刻化する中、これは経営インパクトの大きい改善です。

また、2048ビット化は単体性能だけでなく、将来のスケール戦略にも影響します。GPUあたりのHBM容量が48GB〜64GBへ拡張する中、広帯域インターフェースは大容量データをリアルタイムに処理するための前提条件となります。

HBM4の登場によって、メモリは受動的なデータ格納装置から、AIアーキテクチャ全体のパフォーマンスを規定する「戦略的レイヤー」へと位置づけが変わりました。2048ビットと2TB/s級帯域は、その象徴的なマイルストーンといえます。

ロジック・ベースダイがもたらすニアメモリ/インメモリコンピューティング

HBM4で最も本質的な変化は、ベースダイが単なる接続基板から、先端ロジックプロセスを用いた“演算可能な層”へと進化した点にあります。SKハイニックスはTSMCの12nm、サムスン電子は4nmプロセスをベースダイに採用し、メモリスタックの最下層に高度な制御回路や演算ブロックを実装しています。

この構造転換により現実味を帯びてきたのが、ニアメモリ・コンピューティング(NMC)およびインメモリ・コンピューティング(IMC)です。従来はGPUやASICがすべての演算を担い、HBMはデータを供給する受動的存在でした。しかしHBM4世代では、**メモリ側で前処理や一部演算を実行し、データ移動そのものを減らす設計思想**へと移行しています。

Semiconductor Engineeringの報告によれば、2048ビット化された広帯域インターフェースとロジックベースダイの組み合わせは、単なる帯域向上ではなく、システムレベルでのレイテンシとエネルギー効率を同時に改善する基盤技術と位置づけられています。

| 項目 | 従来HBM | HBM4(ロジックベースダイ) |

|---|---|---|

| ベースダイ | メモリプロセス中心 | 先端ロジックプロセス採用 |

| 主な役割 | 信号中継・電源管理 | ECC・制御・一部演算処理 |

| データフロー | GPU往復前提 | メモリ内で前処理 |

具体的には、誤り訂正(ECC)やアドレス変換、特定の浮動小数点演算をベースダイ側で実行することで、GPUとのデータ往復回数を削減できます。HBM3E比でスタックあたり2TB/s級へ拡張された帯域と組み合わせることで、AI学習時のボトルネックであった「メモリの壁」を構造的に緩和します。

とりわけエージェント型AIのように長大なコンテキストを保持し続けるワークロードでは、**演算よりもデータ移動の電力コストが支配的になる場面が増えています**。ビットあたりエネルギーを抑えつつ、必要な前処理をメモリ側で完結させる設計は、データセンターの総消費電力抑制にも直結します。

今後は、より複雑な演算ブロックやAI推論特化回路をベースダイに統合する動きも想定されます。ただし発熱や歩留まり、コストとのトレードオフは依然として大きく、どこまでをメモリ側で処理するかはアーキテクチャ設計の競争領域です。

2026年時点で明確なのは、HBM4のロジック化がアクセラレータ設計の自由度を広げ、プロセッサ中心だった計算モデルを再定義し始めているという事実です。ニアメモリ/インメモリコンピューティングは、もはや研究テーマではなく、最先端AI基盤を支える実装技術へと移行しています。

16層積層と30μm薄化の限界突破――製造現場のリアル

16層積層と30μm薄化は、スペック表の数字以上に製造現場へ強烈なプレッシャーを与えています。JEDECがパッケージ全高制限を720μmから775μmへ緩和したとはいえ、その余白はわずかです。16枚のDRAMダイとベースダイ、接合層をこの高さに収めるには、各ダイを約30μmまで削り込む必要があります。

SKハイニックスがCES 2026で公開した16-Hi HBM4は、まさにその極限設計の象徴です。従来の12層HBM3Eでは約50μmだったダイ厚が、HBM4では約30μmへと一気に薄くなっています。ここに製造現場の難易度が凝縮されています。

| 項目 | 12層 HBM3E | 16層 HBM4 |

|---|---|---|

| ダイ厚 | 約50μm | 約30μm |

| 総高さ制限 | 720μm | 775μm |

| 主なリスク | 反り・応力集中 | 破損・アライメント誤差拡大 |

30μmという厚みは、人の髪の毛の半分以下です。この領域では、ウェハの反り(ワーページ)が数十μm単位で発生するだけで、後工程のアライメント精度に致命的な影響を及ぼします。Semiconductor Engineeringによれば、16層世代では微小な熱応力の蓄積が歩留まりを大きく左右すると指摘されています。

特に問題となるのが、薄化工程後のハンドリングです。ディスコが展開する30μm級対応のドライポリッシング技術は、微細ダイでも機械的強度を維持するための重要な基盤です。わずかなクラックやチッピングが、最終的に16枚すべてを無駄にしてしまうためです。

このリスクに対抗するため、積層前検査の重要性も飛躍的に高まっています。アドバンテストのHA1200のようなダイレベル100%検査体制は、Known Good Dieのみを積層する前提条件になりつつあります。検査を強化しなければ、積層数の増加はそのまま歩留まりの指数関数的悪化につながります。

接合技術でも現場は揺れています。2026年時点ではHBM4の多くが従来型マイクロバンプを継続採用していますが、ハイブリッドボンディングへの移行圧力は確実に高まっています。MDPIのレビュー論文では、ハイブリッドボンディングにより接合部の熱抵抗を最大約47%削減できる可能性が示されています。

しかし、TrendForceの報告が示す通り、初期のハイブリッドボンディング量産では歩留まりが課題となっており、理論値と量産現実のギャップが依然として存在します。高さ制限、熱拡散、コスト、設備投資――すべてを同時に満たす解はまだ完成していません。

16層化と30μm薄化は、単なる高性能化ではなく、材料・装置・検査の総力戦です。 ナノレベルの誤差管理、応力制御、熱設計が複雑に絡み合う中で、製造現場は日々“限界値の更新”を続けています。HBM4の真価は帯域幅だけでなく、この極限プロセスを量産レベルで成立させられるかどうかにかかっています。

ハイブリッドボンディングの可能性と量産課題

HBMの進化を語る上で、ハイブリッドボンディングは避けて通れないテーマです。従来のマイクロバンプ接合に代わり、銅と銅を直接接合するこの技術は、積層構造そのものの前提を覆すポテンシャルを持っています。

Semiconductor Engineeringによれば、2026年時点のHBM4では依然としてマイクロバンプ方式が主流ですが、業界はすでにその次を見据えています。ハイブリッドボンディングは、単なる微細化技術ではなく、熱・電気・機械特性を同時に最適化する「接合革命」とも言える存在です。

技術的な優位性は、研究データにも裏付けられています。MDPIに掲載されたレビュー論文では、ハイブリッドボンディング採用時、接合部の熱抵抗が22.8%から最大47%低減し、垂直方向の熱伝導率が最大3倍に向上する可能性が示されています。これは発熱密度が極端に高いAIアクセラレータにとって決定的な差となります。

| 比較項目 | マイクロバンプ | ハイブリッドボンディング |

|---|---|---|

| 接合構造 | はんだバンプ介在 | Cu-Cu直接接合 |

| 接合高さ | 数µmレベル | ほぼゼロに近接 |

| 熱抵抗 | 相対的に高い | 最大約47%低減報告 |

| 将来拡張性 | 微細化に物理的限界 | 高層化に有利 |

しかし、可能性と現実の間には大きな溝があります。TrendForceの報告では、16層HBM4におけるハイブリッドボンディングの初期歩留まりは約10%前後にとどまるとされ、量産適用にはなお時間が必要とされています。

歩留まりを阻む最大の要因は、サブミクロン精度でのアライメントと表面平坦性の確保です。わずかなパーティクルや酸化膜の不均一が、全スタック不良につながります。16枚積層では1枚の欠陥が全体を無価値化するため、従来以上にプロセス制御の難易度が跳ね上がります。

さらに設備投資も重い負担です。ハイブリッドボンディング対応の接合装置や前処理装置は高額であり、既存のマイクロバンプラインとの二重投資が必要になります。このため、2026年時点ではSKハイニックスが実績あるMR-MUFを継続し、次世代以降での本格移行を見据える戦略を取っている点は合理的です。

一方で、ロジックベースダイ化が進むHBMでは、将来的にウェハ・ツー・ウェハ接合との親和性が高いハイブリッドボンディングが有利になる可能性が高いです。AIチップがさらに高発熱・高帯域化する中で、**熱と電気のボトルネックを同時に解消できる唯一の実装技術**として、その存在感は確実に増しています。

量産課題をどう克服するかは、単なる製造技術の問題ではありません。HBMの供給能力、コスト構造、さらにはAIインフラの拡張速度そのものを左右する戦略的テーマになっています。2026年は本格普及には至らなかったものの、ハイブリッドボンディングが「選択肢」から「不可避の進化」へと変わる転換点に立っている年だと言えます。

日本企業が握るチョークポイント:材料・装置・検査の最前線

HBM4の量産が現実味を帯びる2026年、日本企業は材料・装置・検査という三つの領域で明確なチョークポイントを握っています。これは単なる部材供給ではなく、歩留まりと熱、そして信頼性を左右する“不可欠な工程”を押さえているという意味での戦略的優位です。

とりわけ材料分野では、レゾナックがHBM積層に用いられる非導電性フィルム(NCF)で世界シェア約50%を占めています。The Japan Timesによれば、同社はAI半導体材料強化に向けて生産能力を大幅に増強しており、16層HBM4の拡大はそのまま需要増に直結します。

16層化では絶縁層の均一性や熱拡散特性が一段と重要になります。レゾナックは横浜国立大学との連携やJOINT3コンソーシアムを通じ、垂直配向カーボンを用いた次世代TIM開発を進めています。これは高発熱化するHBM4世代での熱ボトルネック解消を狙ったものです。

| 分野 | 主要企業 | 戦略的意義 |

|---|---|---|

| 材料 | レゾナック | NCF世界シェア約50%、16層化で需要拡大 |

| 研削 | ディスコ | 30μm級薄化を支えるドライポリッシング |

| 検査 | アドバンテスト | HBM専用テスタでKGD選別を高度化 |

| 装置 | 東京エレクトロン | TSV・先端接合でサブミクロン精度 |

装置分野では、東京エレクトロンがTSV形成や先端パッケージ工程で存在感を示しています。同社の技術ブログでも触れられている通り、反り補正や高精度アライメントは16層積層での歩留まり確保に直結します。ハイブリッドボンディングを見据えた装置開発も進み、将来世代への布石となっています。

また、ディスコの30μm級ウェハ研削技術はHBM4の前提条件です。極薄化に伴うワーページや破損リスクを抑える同社のDP26ドライポリッシングは、超高積層構造の量産を支える基盤技術です。

検査領域ではアドバンテストがHBMテスタ市場で過半シェアを握ります。HA1200のようなハンドラによりダイ段階での厳格な選別が可能となり、1枚の不良が16枚全体を無価値にするリスクを事前に遮断します。これはAI向け高単価製品において極めて大きな経済的意味を持ちます。

2026年のメモリ・スーパーサイクルの裏側で、日本企業は“黒子”としてではなく、AIインフラの根幹を支える構造的プレイヤーへと位置付けを高めています。代替困難な工程を押さえることこそが、真のチョークポイント戦略なのです。

NVIDIA Rubinとエージェント型AIが押し上げるHBM需要

2026年、HBM需要を決定的に押し上げているのが、NVIDIAの次世代アーキテクチャ「Rubin」と、自律的に思考・行動するエージェント型AIの本格普及です。単なる性能向上ではなく、AIの使われ方そのものが変わったことが、メモリ需要の質と量を同時に引き上げています。

CES 2026で発表されたRubinは、TSMCの3nmプロセスで製造され、3,360億トランジスタを搭載します。前世代Blackwellと比較して飛躍的に演算密度を高め、その能力を引き出すためにHBM4を全面採用しました。

| 世代 | 採用HBM | メモリ帯域幅 | 推論性能(NVFP4) |

|---|---|---|---|

| Blackwell(2024) | HBM3E | 10TB/s | 10PFLOPS |

| Rubin(2026) | HBM4 | 22TB/s | 50PFLOPS |

帯域幅は22TB/sへと倍増以上に拡張され、推論性能は50PFLOPSに到達しました。EE Timesなどの報道によれば、HBM4の2048ビット・インターフェースがこの帯域を支えています。演算性能の進化は、もはやHBMなしには成立しない構造になっています。

さらに重要なのが、RubinがArmベースのVera CPUと統合され、72基のGPUをNVLink 6で束ねるラックスケール構成を前提としている点です。これにより1兆パラメータ級モデルの推論コストを従来比で10分の1に圧縮したとされています。コスト低減は、より多くの事業者が大規模AIを導入する誘因となり、結果としてHBMの需要総量を拡大させています。

そして2026年の決定的な変化が、エージェント型AIの実用化です。従来のチャット型AIと異なり、エージェントは長時間にわたりタスクを遂行し、数百万トークン規模のコンテキストを保持します。Markets系レポートが指摘する通り、この動作にはGPUあたり512GB超の大容量メモリが不可欠です。

HBM4ではスタックあたり最大48〜64GB、16層構成による高容量化が進み、外部ストレージへの頻繁なスワップを回避できます。これによりレイテンシが抑制され、リアルタイムでの自律的意思決定が可能になります。

結果として、HBMは単なる高速メモリではなく、AIエージェントの「作業記憶」を担う中核資産となりました。Rubin世代のGPU出荷拡大とエージェント型AIの企業導入が同時進行する2026年は、HBM需要が構造的に上方シフトした転換点と位置づけられます。

車載・エッジAIへの波及とGDDR7/LPDDR6との棲み分け

HBM4の主戦場は依然としてデータセンターですが、その技術的波及は車載・エッジAIにも確実に広がっています。ただし重要なのは、すべてがHBMに置き換わるわけではないという点です。2026年は、用途ごとの最適メモリを選択する「戦略的棲み分け」が明確になった年でもあります。

S&P GlobalやFrost & Sullivanの分析によれば、自動車業界はソフトウェア定義車両からAI定義車両へと急速に移行しています。NVIDIAのDRIVE AGX Thorは最大2,000 TOPS級の演算性能を持ち、レベル4自動運転や車内LLM実行を視野に入れた設計です。このクラスではセンサーフュージョンとリアルタイム推論を同時並行で処理するため、帯域とレイテンシが安全性に直結します。

TechInsightsの2026年メモリ展望でも、車載向け高性能コンピューティングではHBMの採用が限定的ながら拡大傾向にあると指摘されています。特に中央集約型アーキテクチャでは、複数ECUを統合するためメモリ帯域需要が急増しています。

| 規格 | 主用途 | 技術的特性(2026年) |

|---|---|---|

| HBM4 | 自動運転中枢・AI学習 | 最大約2TB/s/スタック、超低レイテンシ |

| GDDR7 | エッジ推論・車載演算補助 | 最大48Gbps、コスト効率の高い広帯域 |

| LPDDR6 | IVI・モバイルAI | 14.4Gbps、低消費電力・高集積 |

一方、すべての車載AIがHBMを必要とするわけではありません。ADASの一部機能やインフォテインメント領域では、電力効率とコストがより重要です。Semiconductor Engineeringが指摘する通り、エッジ推論用途ではGDDR7が性能と価格のバランスに優れ、LPDDR6は待機電力の低さから常時稼働系アプリケーションに適しています。

特にスマートフォンや産業用エッジデバイスでは、物理サイズと熱設計の制約が厳しく、HBMの3D積層構造は過剰仕様になりやすいです。ISSCC 2026で示された14.4Gbps級LPDDR6や48Gbps級GDDR7は、オンデバイスAIの推論処理を現実的な消費電力内で実現する選択肢として存在感を高めています。

巨大LLMの学習や超大規模推論はHBM4が担い、車両の中枢AIや一部高信頼領域で限定採用が進みます。その周辺をGDDR7が支え、常時接続・低電力領域をLPDDR6が担う。こうした階層構造が確立したことで、AIはデータセンターからクルマ、そして手のひらのデバイスへと、現実的なコスト構造の中で広がり始めています。

米中輸出規制と中国勢の台頭がもたらすサプライチェーン再編

米中輸出規制の強化と中国勢の台頭は、HBMを中核とするAI半導体サプライチェーンを根本から組み替えつつあります。2026年1月、米商務省産業安全保障局(BIS)は先端AIチップの対中輸出規則を改定し、一定スペック未満の製品に限り個別審査を認める枠組みを導入しました。

具体的には、TPP21,000未満かつ帯域幅6,500GB/s未満の製品が審査対象となり、さらに25%の関税や第三者認証要件が課されます。Morgan LewisやCovingtonの分析によれば、これは全面禁止から「精緻化」への転換ですが、実務上のコンプライアンス負担はむしろ増大しています。

| 規制項目 | 主な内容 | 影響 |

|---|---|---|

| 性能基準 | TPP・帯域幅に上限設定 | 旧世代品に限定的輸出余地 |

| 関税措置 | 対象品に25%関税 | 再輸出コスト上昇 |

| 認証義務 | 第三者検証を要求 | 供給リードタイム長期化 |

この結果、**最先端HBM4を搭載するAIアクセラレータは事実上、米国・同盟圏向けに優先配分される構図**が鮮明になっています。Foundry条項により米国顧客向け供給の優先証明が求められ、製造キャパシティの囲い込みが進んでいます。

一方、中国ではChangXin Memory Technologies(CXMT)が約42億ドルを調達し、2026年末までのHBM量産を目指しています。TechInsightsなどが指摘する通り、中国勢は熱管理や動作速度でなお1~2世代の差がありますが、国内AI需要を背景に垂直統合型の供給網構築を急いでいます。

特に注目すべきは、ファーウェイを含む中国企業が自国設計のAIチップと国産メモリの組み合わせを模索している点です。これは単なる代替ではなく、**「規制耐性」を前提としたサプライチェーン設計への転換**を意味します。

その結果、HBMを巡る世界の供給網は三層構造へと再編されています。第一層は米国・韓国・日本・台湾を軸とする最先端帯域ゾーン、第二層は規制閾値直下の調整型製品ゾーン、第三層は中国国内循環型ゾーンです。

この分断は単なる地政学リスクではなく、価格形成や投資判断にも直結します。最先端HBMの価格プレミアムが維持される一方で、規制適合モデルは仕様最適化という新たな設計競争を生んでいます。

AIインフラが国家戦略そのものとなった2026年、サプライチェーンは効率最優先のグローバル最適化から、安全保障を織り込んだリージョナル最適化へと移行しています。HBMはその最前線で、技術だけでなく地政学によっても進化の方向を規定されているのです。

HBM4以降のロードマップ:HBM4E・HBM5と光インターコネクトの展望

HBM4が本格立ち上げを迎えた2026年、業界の視線はすでに次世代であるHBM4EおよびHBM5へと移っています。単なる帯域幅の延長線ではなく、メモリとインターコネクトを含めた「システム全体の再設計」がロードマップの中心に据えられつつあります。

HBM4Eは2027年以降の投入が見込まれ、HBM4の2048ビット・インターフェースを踏襲しながら、さらなるピン速度向上と歩留まり改善を狙う強化版という位置づけです。一方でHBM5では、積層数の増加やハイブリッドボンディングの本格適用が議論されています。

| 世代 | 想定時期 | 技術的焦点 |

|---|---|---|

| HBM4E | 2027年前後 | 高速化・電力効率最適化、先端パッケージ適合 |

| HBM5 | 2028年以降 | さらなる高層化、ハイブリッドボンディング本格化 |

Semiconductor Engineeringによれば、HBM4世代では依然としてマイクロバンプ技術が主流ですが、HBM4E以降で銅-銅直接接合への移行圧力が一段と強まると指摘されています。熱抵抗低減や接続密度向上の観点から、3D積層の物理限界を押し広げる鍵となるためです。

しかし、真に破壊的なのはメモリそのものよりも「接続」の進化です。NVIDIAがRubin世代でNVLink 6を導入したように、GPU間・ラック間の帯域幅は指数関数的に拡大しています。ここでボトルネックとなるのが電気信号ベースのインターコネクトです。

TechInsightsのメモリ展望レポートでも、2028年前後に光インターコネクトの実装がデータセンター内通信の主流候補になると示唆されています。電気配線に比べ、長距離伝送時の消費電力と信号劣化を大幅に抑制できるためです。

今後想定されるアーキテクチャは、次のような構造です。

この構成が実現すれば、HBM5世代では単体GPUの帯域幅拡張だけでなく、複数GPUをまたいだメモリプール化が加速します。結果として、物理的に分散したHBM資源を論理的に一体化する「ディスアグリゲーテッド・メモリアーキテクチャ」が本格化する可能性があります。

重要なのは、HBMの進化がもはやチップ単体の競争ではなく、パッケージ、基板、光トランシーバー、さらにはデータセンター設計まで巻き込む総力戦に入った点です。HBM4EとHBM5は、その象徴的な転換点として位置づけられています。

参考文献

- SK hynix Newsroom:2026 Market Outlook: SK hynix’s HBM to Fuel AI Memory Boom

- EE Times:The State of HBM4 Chronicled at CES 2026

- TrendForce:NVIDIA Demand Fuels HBM4 Race: 12-Layer Ramps, 16-Layer Push by SK hynix, Samsung and Micron

- Semiconductor Engineering:HBM4 Sticks With Microbumps, Postponing Hybrid Bonding

- The Japan Times:Chip-sector linchpin Resonac seeks to tap China’s AI ambitions

- Advantest:HA1200|Test Handler|ADVANTEST CORPORATION

- Mayer Brown:Administration Policies on Advanced AI Chips Codified, with Reverberations Across AI Ecosystem